#### **Features**

- 1 Hz to 2.5 MHz ±5 ppm all-inclusive frequency stability

- Factory programmable output frequency

- World's smallest TC-MO Footprint: 1.2 mm²

- 1.5 x 0.8 mm CSP

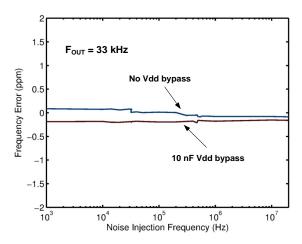

- No external bypass cap required

- Improved stability reduces system power with fewer network timekeeping updates

- Ultra-low power: +6.0 µA (100 kHz)Supply voltage: +1.62 V to +3.63 V

- Operating temperature ranges: -20°C to +70°C, -40°C to +85°C

- Pb-free, RoHS and REACH compliant

#### **Applications**

- Health and wellness monitors

- Smart pens

- ULP input devices

- Proprietary wireless

- Sensor interface

Pb-Fr€

RoHS Compliant

#### **Table 1. Electrical Characteristics**

Conditions: Min/Max limits are over temperature, Vdd = +1.8V ±10%, unless otherwise stated. Typicals are at +25°C and Vdd = +1.8V.

| Parameter                     | Symbol                  | Min.  | Тур.               | Max.               | Unit              | Condition                                                                                                                                                                    |  |  |  |

|-------------------------------|-------------------------|-------|--------------------|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                               | Frequency and Stability |       |                    |                    |                   |                                                                                                                                                                              |  |  |  |

| Output Frequency              | Fout                    | 1     |                    | 2.5M               | Hz                |                                                                                                                                                                              |  |  |  |

| Total Frequency Stability [1] | F_stab                  | -5    |                    | +5                 | ppm               | All inclusive, Stability code: E                                                                                                                                             |  |  |  |

|                               |                         | -20   |                    | +20                | ppm               | All inclusive, Stability code: G                                                                                                                                             |  |  |  |

| Allan Deviation               | AD                      |       | 1e-8               | 4e-8               |                   | 1 second averaging time                                                                                                                                                      |  |  |  |

| First Year Frequency Aging    | F_aging                 |       | ±1                 |                    | ppm               | $T_A = +25$ °C, Vdd = +1.8V                                                                                                                                                  |  |  |  |

|                               | Jitter Performance      |       |                    |                    |                   |                                                                                                                                                                              |  |  |  |

| Integrated Phase Jitter       | IPJ                     |       | 2                  | 3.5                | ns <sub>RMS</sub> | F <sub>OUT</sub> > 1 kHz. Integration bandwidth = 100 Hz to F <sub>OUT</sub> /2. Inclusive of +50 mV peak-to-peak sinusoidal noise on Vdd. Noise frequency 100 Hz to 20 MHz. |  |  |  |

| Period Jitter                 | PJ                      |       | 2.2                | 4.5                | $ns_{RMS}$        | Cycles = 10,000, f = 100kHz. Per JEDEC standard 65B, tested at                                                                                                               |  |  |  |

| Peak-to-Peak Period Jitter    | PJ <sub>p-p</sub>       |       | 20                 | 35                 | ns <sub>p-p</sub> | 100kHz. See performance plot for other frequencies.                                                                                                                          |  |  |  |

|                               |                         |       | Supply Volt        | age and Cu         | rrent Cons        | sumption                                                                                                                                                                     |  |  |  |

| Operating Supply Voltage      | Vdd                     | +1.62 |                    | +3.63              | V                 |                                                                                                                                                                              |  |  |  |

|                               |                         |       | +3.65              | +5                 |                   | F <sub>OUT</sub> = 1 Hz, Vdd = +1.8V, no load                                                                                                                                |  |  |  |

|                               | ldd                     |       | +4.5               | +5.5               | μΑ                | F <sub>OUT</sub> = 33 kHz, Vdd = +1.8V, no load                                                                                                                              |  |  |  |

| Supply Current                |                         |       | +6.0               | +10                |                   | F <sub>OUT</sub> = 100 kHz, Vdd = +1.8V, no load                                                                                                                             |  |  |  |

|                               |                         |       | +13                | +20                |                   | F <sub>OUT</sub> = 1 MHz, Vdd = +1.8V, no load                                                                                                                               |  |  |  |

|                               |                         |       | +33                | +40                |                   | F <sub>OUT</sub> = 2 MHz, Vdd = +1.8V, no load                                                                                                                               |  |  |  |

|                               | t_start                 |       | 150                | 300                | ms                | Fout > 200 Hz.  Measured when supply reaches 90% of final Vdd to the first output pulse and within specified min/max frequency limit.                                        |  |  |  |

| Start-up Time at Power-up     |                         |       | 300+<br>2.0 cycles | 300+<br>2.5 cycles |                   | 10 Hz < Fout ≤ 200 Hz.  Measured when supply reaches 90% of final Vdd to the first output pulse and within specified min/max frequency limit.                                |  |  |  |

|                               |                         |       |                    | 500+               |                   | 1 Hz ≤ Fout ≤ 10 Hz.                                                                                                                                                         |  |  |  |

|                               |                         |       |                    | 2.5 cycles         |                   | Measured when supply reaches 90% of final Vdd to the first output pulse and within specified min/max frequency limit.                                                        |  |  |  |

|                               | Г                       |       | Opera              | ting Tempe         |                   | nge                                                                                                                                                                          |  |  |  |

| Operating Temperature Range   | Op_Temp                 | -20   |                    | +70                | °C                | "D" ordering code                                                                                                                                                            |  |  |  |

| operating reinperature (tange | - F                     | -40   |                    | +85                | °C                | "I" ordering code                                                                                                                                                            |  |  |  |

|                               | <u> </u>                |       | 1                  | LVCMOS             | Output            |                                                                                                                                                                              |  |  |  |

| Output Rise/Fall Time         | tr, tf                  |       | 9                  | 20                 | ns                | 20-80%, 15 pF Load, Vdd = 1.8 +/- 10%                                                                                                                                        |  |  |  |

| Output Clock Duty Cycle       | DC                      | 45    |                    | 55                 | %                 |                                                                                                                                                                              |  |  |  |

| Output Voltage High           | VOH                     | 90%   |                    |                    | Vdd               | I <sub>OH</sub> = -50 μA, 15pF load                                                                                                                                          |  |  |  |

| Output Voltage Low            | VOL                     |       |                    | 10%                | Vdd               | I <sub>OL</sub> = +50 μA 15pF load                                                                                                                                           |  |  |  |

#### Note:

Includes initial tolerance, over temp stability, 2x reflow, Vdd range, board-level underfill, and 20% load variation. Tested with Agilent 53132A frequency counter. Measured with ≥100 ms gate time for accurate frequency measurement.

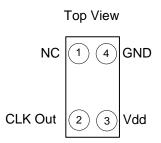

## **Table 2. Pin Configuration**

| CSP<br>Pin | Symbol  | I/O                    | Functionality                                                                                                                                                                                                   |

|------------|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NC      | Internal Test          | No Connect. Leave floating. Pin 1 is for internal testing and is designed to be left floating.                                                                                                                  |

| 2          | CLK Out | OUT                    | Oscillator clock output.                                                                                                                                                                                        |

| 3          | Vdd     | Power Supply           | Operates from nominal supply voltages between +1.8V and +3.3V.<br>Under normal operating conditions, Vdd does not require external<br>bypass/decoupling capacitor(s).<br>MO1576 includes on-chip Vdd filtering. |

| 4          | GND     | Power Supply<br>Ground | Connect to ground.                                                                                                                                                                                              |

Figure 1.Pin Assignment

## **Table3. Absolute Maximum Ratings**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part.

Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameters                                         | Test Conditions      | Value        | Unit |

|----------------------------------------------------|----------------------|--------------|------|

| Continuous Power Supply Voltage Range (Vdd)        |                      | -0.5 to +4.0 | V    |

| Continuous Maximum Operating Temperature Range     |                      | +105         | °C   |

| Short Duration Maximum Operating Temperature Range | ≤ 30 minutes         | +125         | °C   |

| Human Body Model (HBM) ESD Protection              | JESD22-A114          | +2000        | V    |

| Charge-Device Model (CDM) ESD Protection           | JESD22-C101          | +750         | V    |

| Machine Model (MM) ESD Protection                  | JESD22-A115          | +300         | V    |

| Latch-up Tolerance                                 | JESD78               | 3 Compliant  |      |

| Mechanical Shock Resistance                        | Mil 883, Method 2002 | 20,000       | g    |

| Mechanical Vibration Resistance                    | Mil 883, Method 2007 | 70           | g    |

| 1508 CSP Junction Temperature                      |                      | +150         | °C   |

| Storage Temperature                                |                      | -65 to +150  | °C   |

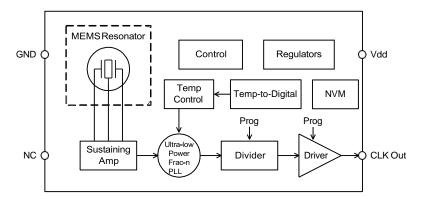

## **System Block Diagram**

Figure 2. MO1576 Block Diagram

#### **Description**

MO1576 is an ultra-small and ultra-low power Factory programmable TC-MO with an output frequency range between 1 Hz to 2.5 MHz. KDS's silicon MEMS technology enables the first 1 Hz - 2.5 MHz TC-MO in the world's smallest footprint and chip-scale packaging (CSP). Typical supply current is only +6.0  $\mu$ A (100 kHz).

KDS's MEMS oscillators consist of MEMS resonators and a programmable analog circuit. MO1576 MEMS resonators is built with unique MEMS First<sup>TM</sup> process. A kev manufacturing step is EpiSeal<sup>TM</sup> during which the MEMS resonator is annealed with temperatures over +1000°C. EpiSeal creates an extremely strong, clean, vacuum chamber that encapsulates the MEMS resonator and ensures the best performance and reliability. During EpiSeal, a poly silicon cap is grown on top of the resonator cavity, which eliminates the need for additional cap wafers or other exotic packaging. As a result. KDS's MEMS resonator die can be used like anv other semiconductor die. One unique result of KDS's MEMS First and EpiSeal manufacturing processes is the capability to integrate KDS's MEMS die with a SOC, ASIC, microprocessor or analog die within a package to eliminate external timing components and provide a highly integrated, smaller, cheaper solution to the customer.

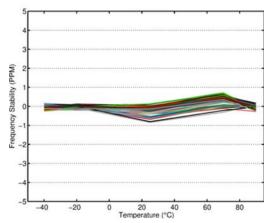

#### TC-MO Frequency Stability

MO1576 is factory calibrated (trimmed) over multiple temperature points to guarantee extremely tight stability over temperature. Unlike quartz crystals that have a classic tuning fork parabola temperature curve with a +25°C turnover point with a 0.04 to 0.06 ppm/°C² temperature coefficient, the MO1576 temperature coefficient is calibrated and corrected over temperature with an active temperature correction circuit. The result is a 32 kHz TC-MO with extremely tight frequency variation over the -40°C to +85°C temperature range.

When measuring the output frequency of MO1576 with a frequency counter, it is important to make sure the counter's gate time is >100 ms. Shorter gate times may lead to inaccurate measurements Similarly, the gate time will need to increase for frequencies in the 1Hz to 500Hz frequency range.

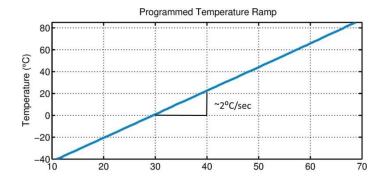

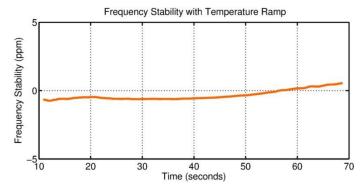

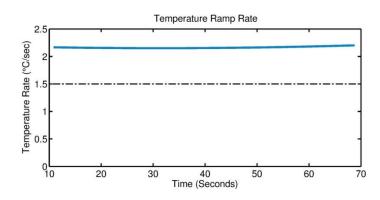

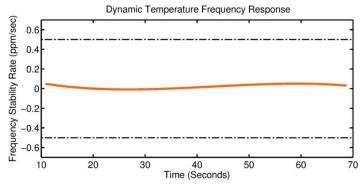

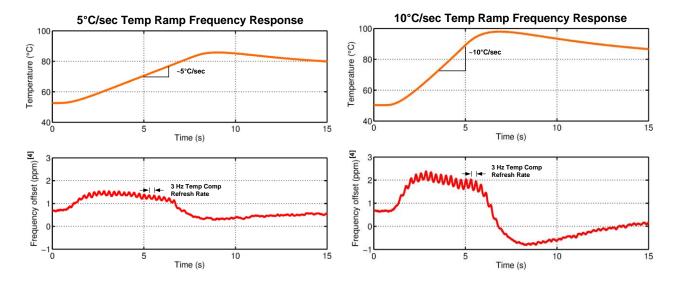

# Dynamic Temperature Frequency Response

Dynamic Temperature Frequency Response is the rate of frequency change during temperature ramps. This is an important performance metric when the oscillator is mounted near a high power component (e.g. SoC or power management) that may rapidly change the temperature of surrounding components.

For moderate temperature ramp rates (<+2°C/sec), the dynamic response is primarily determined by the steady-state frequency vs. temperature of the device. The best dynamic response is obtained from parts which have been trimmed to be flat in frequency over temperature.

For high temperature ramp rates (>+5°C/sec), the latency in the temperature compensation loop contributes a larger frequency error, which is dependent on the temperature compensation update rate. This part achieves excellent performance at 3Hz update rate. This device family supports faster update rates for further reducing dynamic frequency error at the expense of slightly increased current consumption.

#### **Typical Operating Curves**

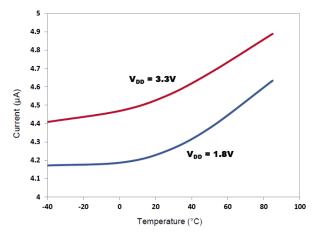

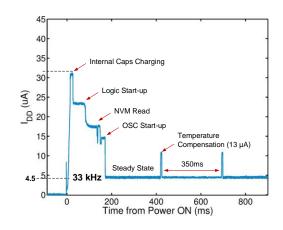

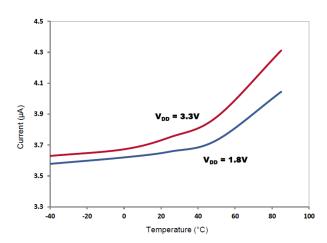

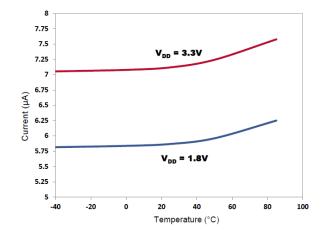

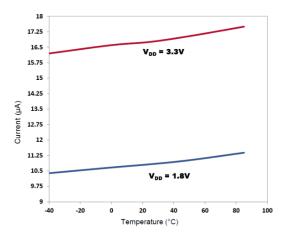

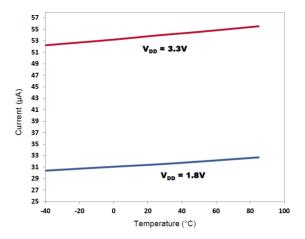

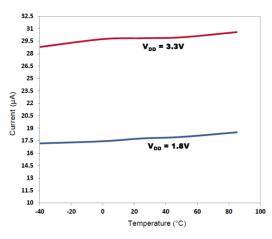

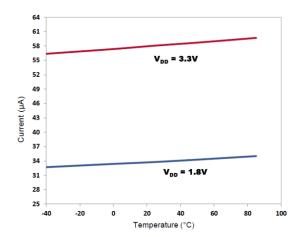

(T<sub>A</sub> = +25°C, Vdd = +1.8V, supply current plots are no load, unless otherwise stated)

Figure 3. Frequency Stability over Temperature

Figure 5. Power Supply Noise Rejection

Figure 7. Supply Current vs Temperature (Fout = 100 Hz)

Figure 4. Start-up and Steady-State Current Profile

Figure 6. Supply Current vs Temperature (Fout = 1 Hz)

Figure 8. Supply Current vs Temperature (Fout = 100 kHz)

Figure 9. Supply Current vs Temperature (Fout = 500 kHz)

Figure 11. Supply Current vs Temperature (Fout = 1.85 MHz)

Figure 10. Supply Current vs Temperature (Fout = 1 MHz)

Figure 12. Supply Current vs Temperature (Fout = 2 MHz)

## **Dynamic Frequency Response for Moderate Temperature Ramps**

Frequency accuracy under a moderate temperature ramp up to 2°C/sec is limited by the TC-MO's trimmed accuracy of the frequency stability over-temperature.

#### Note:

2. Measured relative to 32.768 kHz.

## **Dynamic Frequency Response for Fast Temperature Ramps**

For temperature ramps >+5°C/sec, the frequency accuracy is limited by the update rate of the temperature compensation path (see the +5°C/sec and +10°C/sec plots).

Contact Factory for applications that require improved dynamic performance.

#### Note:

3. Referenced to 32.768 kHz.

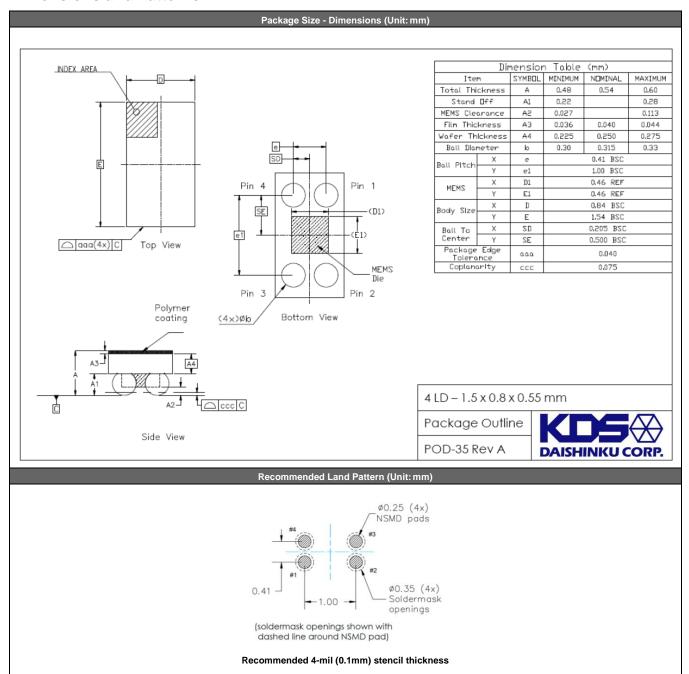

#### **Dimensions and Patterns**

#### **Manufacturing Guidelines**

- 1) No Ultrasonic or Megasonic cleaning: Do not subject MO1576 to an ultrasonic or megasonic cleaning environment. Permanent damage or long term reliability issues may occur.

- 2) Applying board-level underfill and overmold is acceptable and will not impact the reliability of the device.

- 3) Reflow profile, perJESD22-A113D.

- 4) The MO1576 CSP includes a protective, opaque polymer top-coat. If the MO1576 will see intense light, especially in the 1.0-1.2μm IR spectrum, we recommend a protective "glob-top" epoxy or other cover to keep the light from negatively impacting the frequency stability.

- 5) For additional manufacturing guidelines and marking/tape-reel instructions, contact KDS.

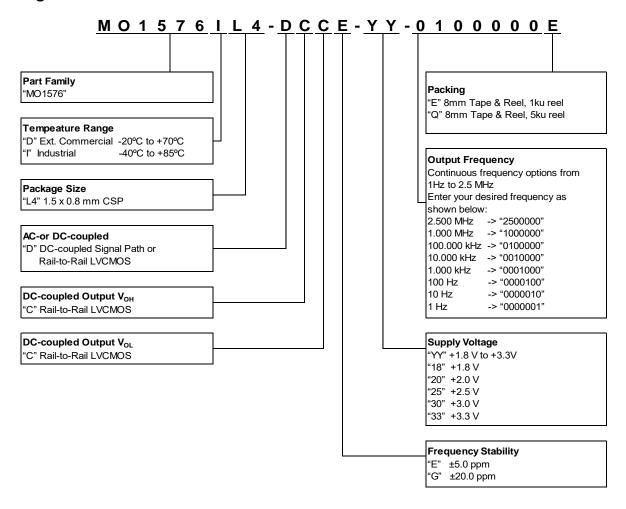

#### **Ordering Information**

## **Table 4. Revision History**

| Revision | Release Date | Change Summary                                                                                                                                                                |  |

|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.25     | 01/13/2016   | Initial Release of Advanced datasheet                                                                                                                                         |  |

| 0.5      | 03/10/2016   | Preliminary datasheet initial release                                                                                                                                         |  |

| 0.9      | 02/15/2017   | Updated Package Outline Drawing (POD) Updated part number ordering information Updated max programmable frequency Updated logo and company address, other page layout changes |  |

| 1.0      | 05/09/2017   | Final Release Updated supply current vs frequency Updated start-up time                                                                                                       |  |

| 1.1      | 06/12/2017   | Updated max operating frequency to 2.0 MHz                                                                                                                                    |  |

| 1.2      | 08/03/2017   | Added additional typical operating curves Updated typical No Load Supply Curren                                                                                               |  |

| 1.3      | 03/15/2018   | Updated max operating frequency from 2.0 MHz to 2.5 MHz                                                                                                                       |  |