### Description

The MO5358 is a ±50 ppb precision MEMS Super-TC-MO engineered for best dynamic performance. It is ideal for high reliability telecom, wireless and networking, industrial, precision GNSS and audio/video applications.

Leveraging KDS's unique DualMEMS<sup>TM</sup> temperature sensing and TurboCompensation<sup>TM</sup> technologies, the MO5358 delivers the best dynamic performance for timing stability in the presence of environmental stressors due to air flow, temperature perturbation, vibration, shock and electromagnetic interference. This device also integrates multiple on-chip regulators to filter power supply noise, eliminating the need for a dedicated external LDO.

The MO5358 offers three device configurations that can be ordered with the associated ordering codes for:

- 1) TC-MO with non-pullable output frequency,

- VCTC-MO allowing voltage control of output frequency,

- DCTC-MO enabling digital control of the output frequency using an I<sup>2</sup>C interface, pullable to 5 ppt (parts per trillion) resolution.

The MO5358 can be factory programmed for any combination of frequency, stability, voltage, and pull range. Programmability enables designers to optimize the clock configuration while eliminating long lead time and customization costs associated with quartz devices where each frequency is custom built.

Refer to Manufacturing Guideline for proper reflow profile and PCB cleaning recommendations to ensure best performance.

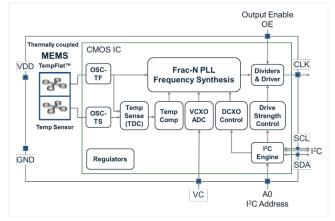

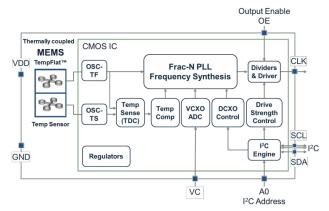

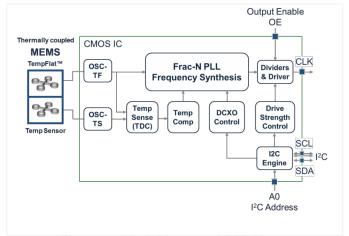

# **Block Diagram**

Figure 1. MO5358 Block Diagram

#### **Features**

- Any frequency between 1 MHz and 60 MHz in 1 Hz steps

- Factory programmable options for low lead time

- Best dynamic stability under airflow, thermal shock

- ±50 ppb over-temperature stability

- ±1 ppb/°C frequency slope (ΔF/ΔT)

- 3e-11 ADEV at 10 second averaging time

- 0°C to +70°C operating temperature

- No activity dips or micro jumps

- Resistant to shock, vibration and board bending

- On-chip regulators eliminate the need for external LDOs

- Digital frequency pulling (DCTC-MO) via I<sup>2</sup>C

- Digital control of output frequency and pull range

- Up to ±3200 ppm pull range

- Frequency pull resolution down to 5 ppt

- **■** +2.5V, +2.8V, +3.0V and +3.3V supply voltage

- LVCMOS or clipped sinewave output

- RoHS and REACH compliant

- Pb-free, Halogen-free and Antimony-free

# **Applications**

- 4G/5G radio, Small cell

- IEEE 1588 boundary and grandmaster clocks

- Synchronous Ethernet

- Optical transport SONET/SDH, OTN, Stratum 3

- DOCSIS 3.x remote PHY

- GPS disciplined oscillators

- Precision GNSS systems

- Test and measurement

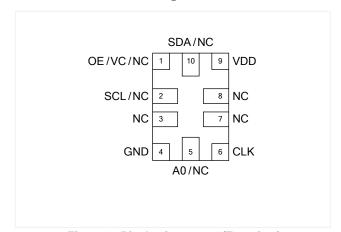

# 5.0 x 3.2 mm<sup>2</sup> Package Pinout

Figure 2. Pin Assignments (Top view) (Refer to Table 11 for Pin Descriptions)

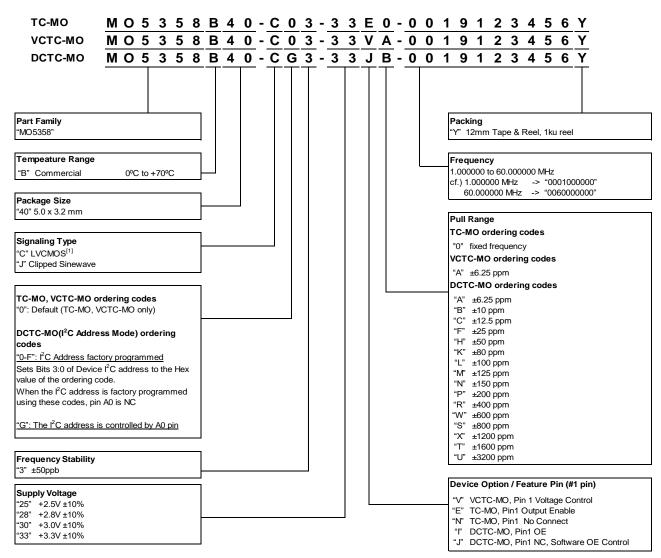

### **Ordering Information**

#### Notes:

<sup>1. &</sup>quot;C" corresponds to the default rise/fall time for LVCMOS output as specified in Table 1 (Electrical Characteristics). Contact KDS for other rise/fall time options for best EMI.

# **TABLE OF CONTENTS**

| Description                                                                               |    |

|-------------------------------------------------------------------------------------------|----|

| Features                                                                                  | 1  |

| Applications                                                                              | 1  |

| Block Diagram                                                                             | 1  |

| 5.0 x 3.2 mm Package Pinout                                                               | 1  |

| Ordering Information                                                                      | 2  |

| Electrical Characteristics                                                                | 4  |

| Device Configurations and Pin-outs                                                        | 8  |

| Pin-out Top Views                                                                         | 8  |

| Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs                             | g  |

| Waveforms                                                                                 | 11 |

| Timing Diagrams                                                                           | 11 |

| Typocal Performance Plots                                                                 | 12 |

| Architecture Overview                                                                     | 16 |

| Frequency Stability                                                                       | 16 |

| Output frequency and format                                                               | 16 |

| Output Frequency Tuning                                                                   | 16 |

| Pin 1 Configuration (OE, VC, or NC)                                                       | 17 |

| Device Cofigurations                                                                      | 17 |

| TC-MO Cofiguration                                                                        | 17 |

| VCTC-MO Cofiguration                                                                      | 18 |

| DCTC-MO Cofiguration                                                                      | 19 |

| VCTC-MO-Specific Design Considerations                                                    | 20 |

| Linearity                                                                                 | 20 |

| Control Volgate Bandwidth                                                                 | 20 |

| FV Characteristic Slope Kv                                                                | 20 |

| Pull Range, Absolute Pull Range                                                           | 21 |

| DCTC-MO-Specific Design Considerations                                                    | 22 |

| Pull Range and Absolute Pull Range                                                        | 22 |

| Output Frequency                                                                          | 23 |

| I <sup>2</sup> C Control Registers                                                        | 25 |

| Register Discriptions                                                                     | 25 |

| Register Address: 0x00. Digital Frequency Control Least Significant Word (LSW)            | 25 |

| Register Address: 0x01. OE Control, Digital Frequency Control Most Significant Word (MSW) | 26 |

| Register Address: 0x02. DIGITAL PULL RANGE CONTROL <sup>[13]</sup>                        | 27 |

| Serial Interface Configuration Discription                                                | 28 |

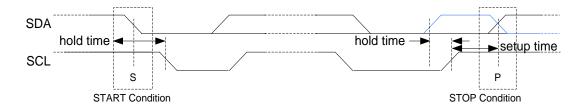

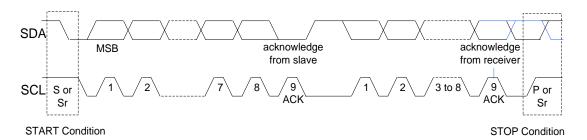

| Serial Signal Format                                                                      | 28 |

| Parallel Signal Format                                                                    | 29 |

| Parallel Data Format                                                                      | 29 |

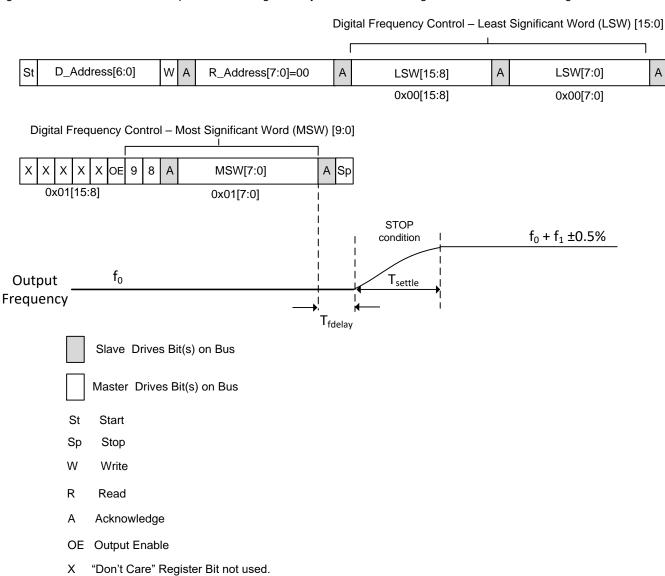

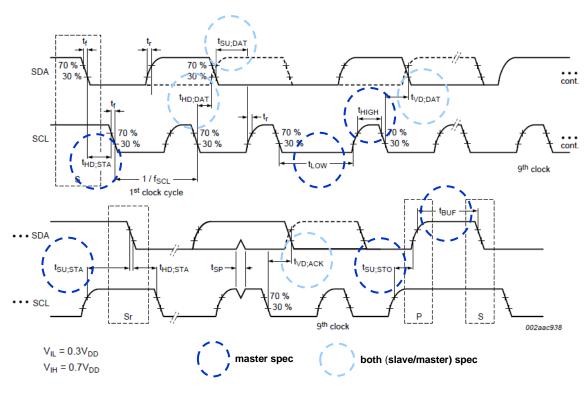

| I <sup>2</sup> C Timing Specification                                                     | 31 |

| I <sup>2</sup> C Device Address Modes                                                     | 32 |

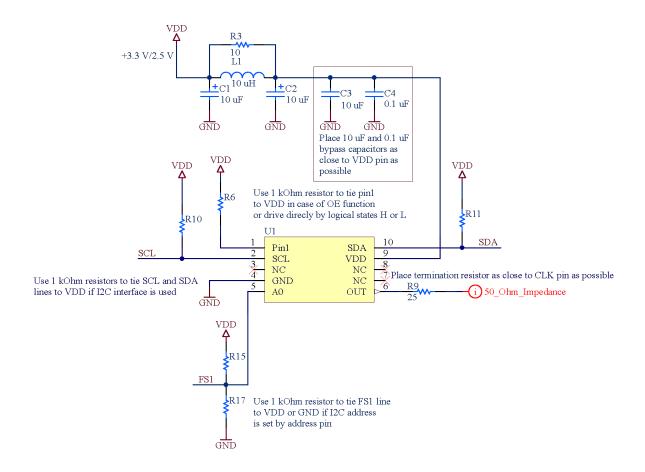

| Schematic Example                                                                         | 33 |

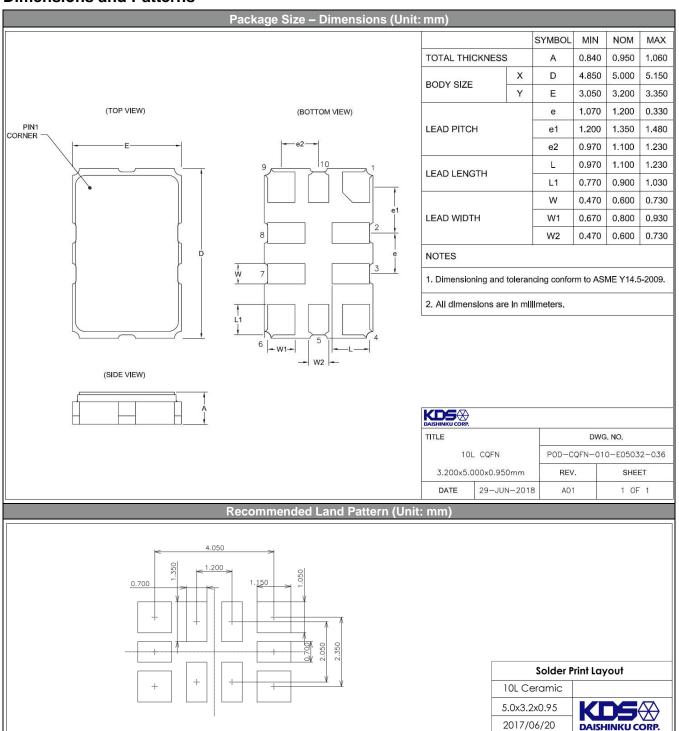

| Dimensions and Patterns                                                                   | 34 |

| Layout Guidelines                                                                         | 35 |

| Manufacturing Guideline                                                                   | 35 |

# **Electrical Characteristics**

All Min and Max limits are specified over temperature and rated operating voltage with 15 pF output load unless otherwise stated. Typical values are at +25°C and +3.3V Vdd

**Table 1. Output Characteristics**

| Parameters                                          | Symbol      | Min.      | Тур.      | Max.         | Unit        | Condition                                                                                                                                   |  |

|-----------------------------------------------------|-------------|-----------|-----------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                     |             |           | Frequenc  | y Coverag    | е           |                                                                                                                                             |  |

| Output Frequency Range                              | F           | 1         | _         | 60           | MHz         |                                                                                                                                             |  |

|                                                     |             |           | Tempera   | ture Range   | е           | ,                                                                                                                                           |  |

| Operating Temperature Range                         | T_use       | 0         | _         | +70          | °C          | Commercial, ambient temperature                                                                                                             |  |

|                                                     |             | Clipped S | inewave O | utput Char   | acteristics |                                                                                                                                             |  |

| Output Voltage Swing                                | V_out       | +0.8      | -         | +1.2         | ٧           | Clipped sinewave output, 10kΩ    10 pF±10%                                                                                                  |  |

| Rises/Fall Time                                     | Tr, Tf      | -         | 3.5       | 4.6          | ns          | 20% - 80% Vdd, F_nom = 19.2 MHz                                                                                                             |  |

|                                                     |             |           | Frequen   | cy Stability | /           |                                                                                                                                             |  |

| Initial Tolerance                                   | F_init      | -0.5      | -         | +0.5         | ppm         | Initial frequency at +25°C inclusive of solder-down shift at 48 hours after 2 reflows                                                       |  |

| Supply Voltage Sensitivity                          | F_Vdd       | -2.5      | ±0.5      | +2.5         | ppb         | Vdd ±5%                                                                                                                                     |  |

| Output Load Sensitivity                             | F_load      | -0.4      | ±0.05     | +0.4         | ppb         | LVCMOS output, 15 pF ±10%. Clipped sinewave output, $10k\Omega \parallel 10 pF \pm 10\%$                                                    |  |

| Frequency Stability over Temperature                | F_stab      | -50       | _         | +50          | ppb         | Referenced to (max frequency+ minimum frequency)/2 over the specified temperature range, Vc = Vdd/2 for VCTC-MO                             |  |

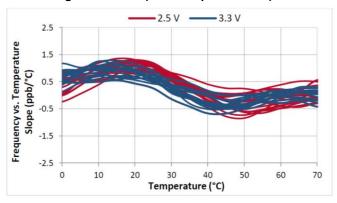

| Frequency vs. Temperature Slope                     | ΔΕ/ΔΤ       | -         | ±0.9      | ±2           | ppb/°C      | 0 to +70°C                                                                                                                                  |  |

| Dynamic Frequency Change during<br>Temperature Ramp | F_dynamic   | -0.02     | ±0.008    | +0.02        | ppb/s       | 0.5°C/min temperature ramp rate                                                                                                             |  |

| 24-hour holdover stability                          | F_24_Hold   | -0.15     | -         | +0.15        | ppm         | Inclusive of over-temp frequency variation                                                                                                  |  |

| Hysteresis Over Temperature                         | F_hys       | -         | ±10       | _            | ppb         | 0 to +70°C , 0.5°C/min ramp rate,                                                                                                           |  |

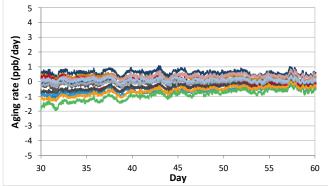

| One-Day Aging                                       | F_1d        | -         | ±1        | -            | ppb         | At +25°C, after 30-days of continued operation. Aging is measured with respect to day 31                                                    |  |

| One-Year Aging                                      | F_1y        | -         | ±0.3      | -            | ppm         | At +25°C, after 2-days of continued operation. Aging is                                                                                     |  |

| 20-Year Aging                                       | F_20y       | _         | ±0.5      | _            | ppm         | measured with respect to day 3                                                                                                              |  |

|                                                     |             | LVC       | MOS Outpu | ut Charact   | eristics    |                                                                                                                                             |  |

| Duty Cycle                                          | DC          | 45        | -         | 55           | %           |                                                                                                                                             |  |

| Rise/Fall Time                                      | Tr, Tf      | 0.8       | 1.2       | 1.9          | ns          | 10% - 90% Vdd                                                                                                                               |  |

| Output Voltage High                                 | VOH         | 90%       | -         | -            | Vdd         | I <sub>OH</sub> = +3 mA                                                                                                                     |  |

| Output Voltage Low                                  | VOL         | -         | -         | 10%          | Vdd         | l <sub>OL</sub> = -3 mA                                                                                                                     |  |

| Start-up Characteristics                            |             |           |           |              |             |                                                                                                                                             |  |

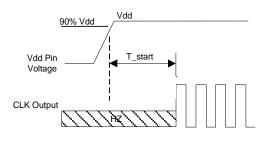

| Start-up Time                                       | T_start     | -         | 2.5       | 3.5          | ms          | Time to first pulse, measured from the time Vdd reaches 90% of its final value.  Vdd ramp time = 100 µs from 0V to Vdd.                     |  |

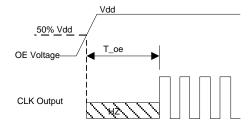

| Output Enable Time                                  | T_oe        | -         | -         | 680          | ns          | F_nom = 10 MHz, See Timing Diagrams section below.                                                                                          |  |

| First Pulse Accuracy                                | T_stability | -         | 5         | 45           | ms          | Time to first accurate pulse within rated stability, measured from the time Vdd reaches 90% of its final value. Vdd ramp time = 100 $\mu s$ |  |

### **Table 2. DC Characteristics**

| Parameters          | Symbol | Min.  | Тур.       | Max.       | Unit | Condition                                            |  |  |

|---------------------|--------|-------|------------|------------|------|------------------------------------------------------|--|--|

| Supply Voltage      |        |       |            |            |      |                                                      |  |  |

|                     |        | +2.25 | +2.5       | +2.75      | V    |                                                      |  |  |

| Supply Voltage      | Vdd    | +2.52 | +2.8       | +3.08      | V    | Contact KDS for +2.25V to +3.63V continuous supply   |  |  |

| Supply Voltage      | vuu    | +2.7  | +3.0       | +3.3       | V    | voltage support                                      |  |  |

|                     |        | +2.97 | +3.3       | +3.63      | V    |                                                      |  |  |

|                     |        |       | Current Co | onsumption | 1    |                                                      |  |  |

| Comment Comments    | ldd    | -     | +44        | +53        | mA   | F = 19.2 MHz, No Load, TC-MO ,DCTC-MO                |  |  |

| Current Consumption |        | _     | +48        | +57        | mA   | F = 19.2 MHz, No Load, VCTC-MO                       |  |  |

| OE Disable Current  | l_od   | 1     | +43        | +51        | mA   | OE = GND, output weakly pulled down , TC-MO, DCTC-MO |  |  |

|                     |        | _     | +47        | +55        | mA   | OE = GND, output weakly pulled down , VCTC-MO        |  |  |

#### **Table 3. Input Characteristics**

| Parameters                         | Symbol                   | Min.                                                                                                                  | Тур.          | Max.        | Unit                      | Condition                                                                                                                                                           |

|------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                          | In                                                                                                                    | put Charac    | teristics - | OE Pin                    | •                                                                                                                                                                   |

| Input Impedance                    | Z_in                     | 75                                                                                                                    | -             | _           | kΩ                        | Internal pull up to Vdd                                                                                                                                             |

| Input High Voltage                 | VIH                      | 70%                                                                                                                   | -             | -           | Vdd                       |                                                                                                                                                                     |

| Input Low Voltage                  | VIL                      | -                                                                                                                     | -             | 30%         | Vdd                       |                                                                                                                                                                     |

|                                    | Freq                     | uency Tur                                                                                                             | ning Range    | - Voltage   | Control or I <sup>2</sup> | C mode                                                                                                                                                              |

|                                    |                          | ±6.25                                                                                                                 | -             | _           | ppm                       | VCTC-MO mode. Contact KDS for ±12.5 and ±25 ppm.                                                                                                                    |

| Pull Range                         | PR                       | ±6.25<br>±10<br>±12.5<br>±25<br>±50<br>±80<br>±100<br>±125<br>±150<br>±200<br>±400<br>±600<br>±1200<br>±1600<br>±3200 | -             | -           | ppm                       | DCTC-MO mode                                                                                                                                                        |

| Absolute Pull Range <sup>[2]</sup> | APR                      | ±5.2                                                                                                                  | -             | -           | ppm                       | DCTC-MO, VCTC-MO for PR = ±6.25 ppm                                                                                                                                 |

| Upper Control Voltage              | VC_U                     | 90%                                                                                                                   | -             | -           | Vdd                       | VCTC-MO mode                                                                                                                                                        |

| Lower Control Voltage              | VC_L                     | -                                                                                                                     | -             | 10%         | Vdd                       | VCTC-MO mode                                                                                                                                                        |

| Control Voltage Input Impedance    | VC_z                     | 8                                                                                                                     | -             | _           | ΜΩ                        | VCTC-MO mode                                                                                                                                                        |

| Control Voltage Input Bandwidth    | VC_bw                    | -                                                                                                                     | 10            | -           | kHz                       | VCTC-MO mode                                                                                                                                                        |

| Frequency Control Polarity         | F_pol                    |                                                                                                                       | Positive      |             |                           | VCTC-MO mode                                                                                                                                                        |

| Pull Range Linearity               | PR_lin                   | _                                                                                                                     | 0.5           | 1.0         | %                         | VCTC-MO mode                                                                                                                                                        |

|                                    | I <sup>2</sup> C Interfa | ace Charac                                                                                                            | cteristics, 2 | 00 Ohm, 5   | 50 pF (Max I              | <sup>2</sup> C Bus Load)                                                                                                                                            |

|                                    |                          | _                                                                                                                     | 100           | _           | kHz                       | -40 to +105°C                                                                                                                                                       |

| Bus Frequency                      | F_I2C                    | _                                                                                                                     | 400           | _           | kHz                       | -40 to +105°C                                                                                                                                                       |

|                                    |                          | _                                                                                                                     | 1000          | _           | kHz                       | -40 to +85°C                                                                                                                                                        |

| Input Voltage Low                  | VIL_I2C                  | _                                                                                                                     | -             | 30%         | Vdd                       | DCTC-MO mode                                                                                                                                                        |

| Input Voltage High                 | VIH_I2C                  | 70%                                                                                                                   | -             | _           | Vdd                       | DCTC-MO mode                                                                                                                                                        |

| Output Voltage Low                 | VOL_I2C                  | -                                                                                                                     | -             | +0.4        | V                         | DCTC-MO mode                                                                                                                                                        |

| Input Leakage current              | lι                       | +0.5                                                                                                                  | -             | +24         | μА                        | 0.1 Vdd <vout<0.9vdd. 200="" current="" dctc-mo="" from="" includes="" kω="" leakage="" mode<="" pull="" resister="" td="" to="" typical="" vdd.=""></vout<0.9vdd.> |

| Input Capacitance                  | CIN                      | -                                                                                                                     | -             | 5           | pF                        | DCTC-MO mode                                                                                                                                                        |

Notes:

2. APR = PR - initial tolerance - 20-year aging - frequency stability over temperature. Refer to Table 17 for APR with respect to other pull rage options.

# Table 4. Jitter & Phase Noise - LVCMOS

| Parameters                 | Symbol    | Min. | Тур. | Max.      | Unit   | Condition                                                              |  |  |  |

|----------------------------|-----------|------|------|-----------|--------|------------------------------------------------------------------------|--|--|--|

| Jitter                     |           |      |      |           |        |                                                                        |  |  |  |

| RMS Phase Jitter (random)  | T_phj     | _    | 0.31 | 0.48      | ps     | F_nom = 10 MHz<br>Integration bandwidth = 12 kHz to 5 MHz              |  |  |  |

| RMS Phase Sitter (random)  | т_рпј     | _    | 0.31 | 0.48      | ps     | F_nom = 50 MH<br>Integration bandwidth = 12 kHz to 20 MHz              |  |  |  |

| RMS Period Jitter          | T_jitt    | -    | 0.8  | 1.1       | ps     | F_nom = 10 MHz, population 10k                                         |  |  |  |

| Peak Cycle-to-Cycle Jitter | T_jitt_cc | -    | 6    | 9         | ps     | F_nom = 10 MHz, population 1k<br>measured as absolute value            |  |  |  |

|                            |           |      | Ph   | ase Noise |        |                                                                        |  |  |  |

| 1 Hz offset                |           | -    | -80  | -74       | dBc/Hz |                                                                        |  |  |  |

| 10 Hz offset               |           | -    | -108 | -102      | dBc/Hz |                                                                        |  |  |  |

| 100 Hz offset              |           | -    | -127 | -123      | dBc/Hz |                                                                        |  |  |  |

| 1 kHz offset               |           | -    | -148 | -145      | dBc/Hz | F_nom = 10 MHz                                                         |  |  |  |

| 10 kHz offset              |           | -    | -154 | -151      | dBc/Hz | TC-MO and DCTC-MO modes, and VCTC-MO mode with<br>±6.25 ppm pull range |  |  |  |

| 100 kHz offset             |           | -    | -154 | -150      | dBc/Hz |                                                                        |  |  |  |

| 1 MHz offset               |           | _    | -167 | -163      | dBc/Hz |                                                                        |  |  |  |

| 5 MHz offset               |           | _    | -168 | -164      | dBc/Hz |                                                                        |  |  |  |

| Spurious                   | T_spur    | _    | -112 | -105      | dBc    | F_nom = 10 MHz, 1 kHz to 5 MHz offsets                                 |  |  |  |

# Table 5. Jitter & Phase Noise - Clipped Sinewave

| Parameters                  | Symbol | Min. | Тур. | Max.       | Unit   | Condition                                                              |  |  |

|-----------------------------|--------|------|------|------------|--------|------------------------------------------------------------------------|--|--|

| Jitter                      |        |      |      |            |        |                                                                        |  |  |

| DMC Phase litter (see down) | T nhi  | -    | 0.31 | 0.45       | ps     | F_nom = 19.2 MHz<br>Integration bandwidth = 12 kHz to 5 MHz            |  |  |

| RMS Phase Jitter (random)   | T_phj  | ı    | 0.31 | 0.48       | ps     | F_nom = 60 MHz<br>Integration bandwidth = 12 kHz to 20 MHz             |  |  |

|                             |        |      | Ph   | nase Noise |        |                                                                        |  |  |

| 1 Hz offset                 |        | -    | -74  | -68        | dBc/Hz |                                                                        |  |  |

| 10 Hz offset                |        | _    | -102 | -97        | dBc/Hz |                                                                        |  |  |

| 100 Hz offset               |        | _    | -121 | -117       | dBc/Hz |                                                                        |  |  |

| 1 kHz offset                |        | _    | -142 | -140       | dBc/Hz | F_nom = 19.2 MHz                                                       |  |  |

| 10 kHz offset               |        | _    | -148 | -146       | dBc/Hz | TC-MO and DCTC-MO modes, and VCTC-MO mode with<br>±6.25 ppm pull range |  |  |

| 100 kHz offset              |        | _    | -149 | -145       | dBc/Hz |                                                                        |  |  |

| 1 MHz offset                |        | -    | -162 | -159       | dBc/Hz |                                                                        |  |  |

| 5 MHz offset                |        | -    | -164 | -160       | dBc/Hz |                                                                        |  |  |

| Spurious                    | T_spur | -    | -109 | -104       | dBc    | F_nom = 19.2 MHz, 1 kHz to 5 MHz offsets                               |  |  |

#### **Table 6. Absolute Maximum Limits**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Test Conditions | Value       | Unit |

|----------------------------------------------------------------------|-----------------|-------------|------|

| Storage Temperature                                                  |                 | -65 to +125 | °C   |

| Continuous Power Supply Voltage Range (Vdd)                          |                 | -0.5 to +4  | V    |

| Human Body Model (HBM) ESD Protection                                | JESD22-A114     | 2000        | V    |

| Soldering Temperature (follow standard Pb-free soldering guidelines) |                 | +260        | °C   |

| Junction Temperature <sup>[3]</sup>                                  |                 | +130        | °C   |

#### Note:

### Table 7. Thermal Considerations<sup>[4]</sup>

| Package                           | θJA<br>(°C/W) | θJC, Bottom<br>(°C/W) |

|-----------------------------------|---------------|-----------------------|

| Ceramic 5.0 x 3.2 mm <sup>2</sup> | 54            | 15                    |

#### Note:

### Table 8. Maximum Operation Junction Temperature<sup>[5]</sup>

| Max Operating Temperature (ambient) | Maximum Operating Junction Temperature |

|-------------------------------------|----------------------------------------|

| +70 °C                              | +80 °C                                 |

#### Note:

5. Datasheet specifications are not guaranteed if junction temperature exceeds the maximum operating junction temperature.

#### **Table 9. Environmental Compliance**

| Parameter                       | Test Conditions           | Value | Unit |

|---------------------------------|---------------------------|-------|------|

| Mechanical Shock Resistance     | MIL-STD-883F, Method 2002 | 10000 | g    |

| Mechanical Vibration Resistance | MIL-STD-883F, Method 2007 | 70    | g    |

| Temperature Cycle               | JESD22, Method A104       | -     | -    |

| Solderability                   | MIL-STD-883F, Method 2003 | -     | -    |

| Moisture Sensitivity Level      | MSL1 @260°C               | -     | _    |

<sup>3.</sup> Exceeding this temperature for an extended period of time may damage the device.

<sup>4.</sup> Measured in still air.

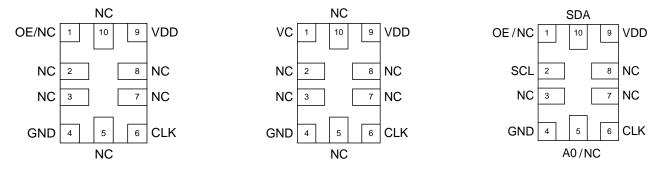

# **Device Configurations and Pin-outs**

### **Table 10. Device Configurations**

| Configuration | Pin 1 | Pin 5 | I <sup>2</sup> C Programmable Parameters                          |

|---------------|-------|-------|-------------------------------------------------------------------|

| TC-MO         | OE/NC | NC    | -                                                                 |

| VCTC-MO       | VC    | NC    | -                                                                 |

| DCTC-MO       | OE/NC | A0/NC | Frequency Pull Range, Frequency Pull Value, Output Enable control |

### **Pin-out Top Views**

Figure 3. TC-MO

Figure 4. VCTC-MO

Figure 5. DCTC-MO

### **Table 11. Pin Description**

| Pin | Symbol                          | I/O                            | Internal Pull-up/Pull Down<br>Resistor | Function                                                                                                                                                                                                                                   |

|-----|---------------------------------|--------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                 | OE – Input                     | 100 kΩ Pull-Up                         | H <sup>[6]</sup> : specified frequency output<br>L: output is high impedance. Only output driver is disabled                                                                                                                               |

| 1   | OE/NC/VC                        | NC <sup>[8]</sup> – No Connect | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

|     |                                 | VC – Input                     | -                                      | Control Voltage in VCTC-MO Mode                                                                                                                                                                                                            |

| 2   | SCL/NC <sup>[8]</sup>           | SCL - Input                    | 200 kΩ Pull-Up                         | I <sup>2</sup> C Serial Clock Input                                                                                                                                                                                                        |

| 2   | SCL/NC <sup>1-3</sup>           | NC – No Connect                | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

| 3   | NC <sup>[8]</sup>               | No Connect                     | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

| 4   | GND                             | Power                          | -                                      | Connect to ground                                                                                                                                                                                                                          |

| 5   | A0/NC <sup>[8]</sup> A0 – Input |                                | 100 kΩ Pull-Up                         | Device I <sup>2</sup> C address when the address selection mode is via the A0 pin. This pin is NC when the I <sup>2</sup> C device address is specified in the ordering code.  A0 Logic Level I <sup>2</sup> C Address 0 1100010 1 1101010 |

|     |                                 | NC – No Connect                | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

| 6   | CLK                             | Output                         | -                                      | LVCMOS, or clipped sinewave oscillator output                                                                                                                                                                                              |

| 7   | NC <sup>[8]</sup>               | No Connect                     | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

| 8   | NC <sup>[8]</sup>               | No Connect                     | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

| 9   | VDD                             | Power                          | -                                      | Connect to VDD <sup>[7]</sup>                                                                                                                                                                                                              |

| 10  |                                 | SDA – Input/Output             | 200 kΩ Pull-Up                         | I <sup>2</sup> C Serial Data.                                                                                                                                                                                                              |

| 10  | SDA/NC <sup>[7]</sup>           | NC - No Connect                | -                                      | H or L or Open: No effect on output frequency or other device functions                                                                                                                                                                    |

#### Notes:

- 6. In OE mode for noisy environments, a pull-up resistor of 10  $k\Omega$  or less is recommended if pin 1 is not externally driven. If pin 1 needs to be left floating, use the NC option.

- 7. 0.1  $\mu$ F capacitor in parallel with a 10  $\mu$ F capacitor are required between Vdd and GND. The 0.1  $\mu$ F capacitor is recommended to place close to the device, and place the 10  $\mu$ F capacitor less than 2 inches away.

- 8. All NC pins can be left floating and do not be soldered down.

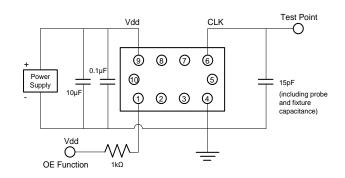

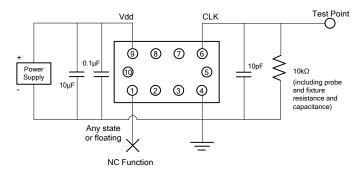

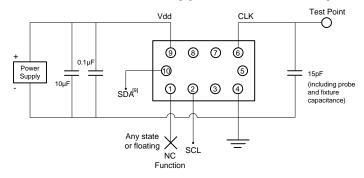

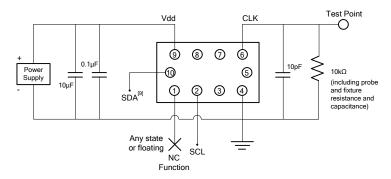

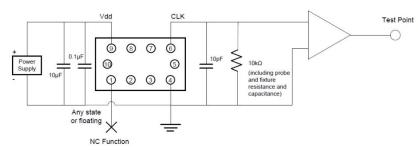

# **Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs**

Figure 6. LVCMOS Test Circuit (OE Function)

Figure 6. LVCMOS Test Circuit (OE Function)

Test Point Vdd CLK  $\cap$ 9 8 7 6 Power Supply 10 (5) 15pF (including probe 1 2 3 4 and fixture capacitance) Control Voltage

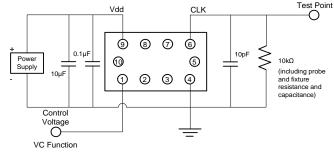

Figure 8. LVCMOS Test Circuit (VC Function)

VC Function

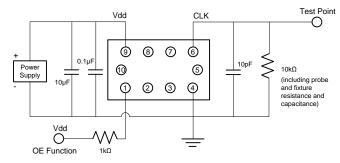

Figure 7. Clipped Sinewave Test Circuit (OE Function)

Figure 9. Clipped Sinewave Test Circuit (VC Function) for AC and DC Measurements

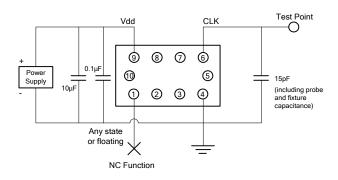

Figure 10. LVCMOS Test Circuit (NC Function)

Figure 11. Clipped Sinewave Test Circuit (NC Function) for AC and DC Measurements

# Test Circuit Diagrams for LVCMOS and Clipped Sinewave Outputs (continued)

Figure 12. LVCMOS Test Circuit (I<sup>2</sup>C Control), DCTC-MO mode

Figure 13. Clipped Sinewave Test Circuit (I<sup>2</sup>C Control), DCTC-MO mode for AC and DC Measurements

Figure 14. Clipped Sinewave Test Circuit for Phase Noise Measurements, Applies to All Configurations (NC Function shown for example only)

#### Notes:

9. SDA is open-drain and may require pull-up resistor if not present in I<sup>2</sup>C test setup.

### **Waveforms**

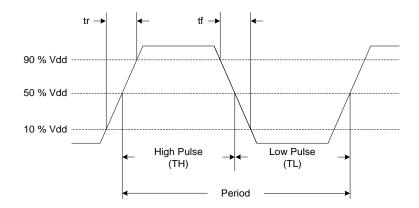

Figure 15. LVCMOS Waveform Diagram<sup>[10]</sup>

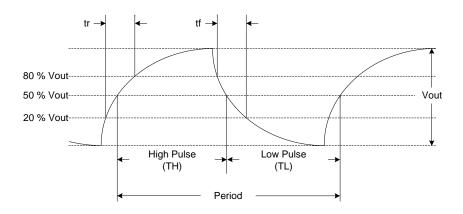

Figure 16. Clipped Sinewave Waveform Diagram<sup>[10]</sup>

#### Notes

10. Duty Cycle is computed as Duty Cycle = TH/Period.

# **Timing Diagrams**

T\_start: Time to start from power-off

Figure 17. Startup Timing

T\_oe: Time to re-enable the clock output

Figure 18. OE Enable Timing (OE Mode Only)

# **Typical Performance Plots**

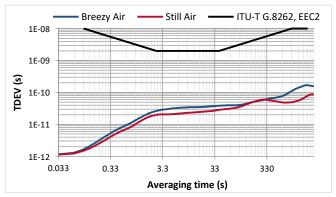

Figure 19. ADEV

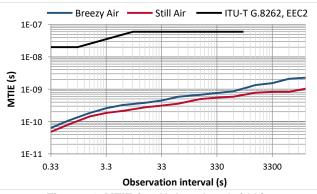

Figure 21. MTIE (0.1 Hz loop bandwidth)

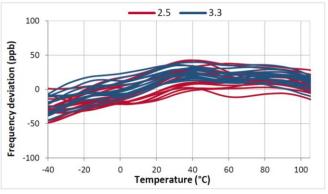

Figure 23. Freq. vs. Temp. Slope (ΔF/ΔT)

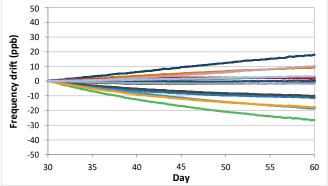

Figure 25. 1-day aging rate (to 62 days)

Figure 20. TDEV (0.1 Hz loop bandwidth)

Figure 22. Frequency vs Temperature

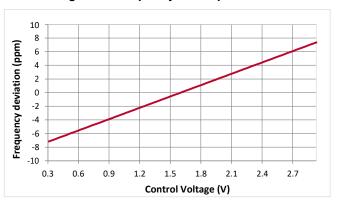

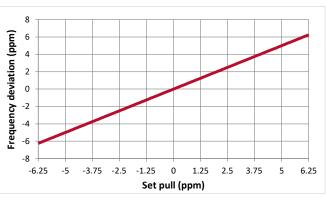

Figure 24. VCTC-MO frequency pull characteristic

Figure 26. Drift over 30 days relative to the first reading

# Typical Performance Plots (continued)

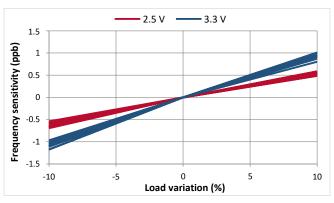

Figure 27. Load sensitivity

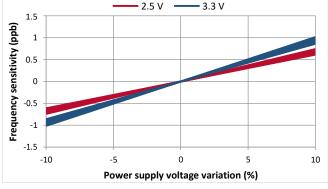

Figure 28. VDD sensitivity

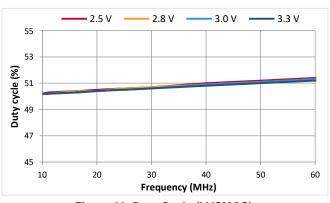

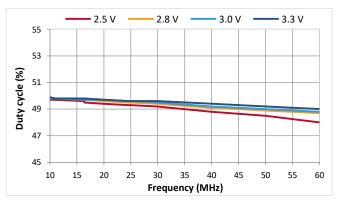

Figure 29. Duty Cycle (LVCMOS)

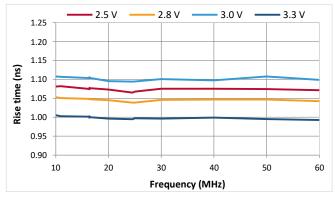

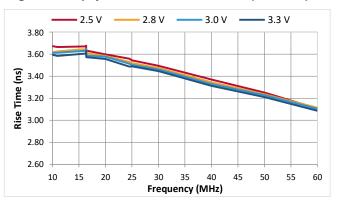

Figure 30. Rise Time (LVCMOS)

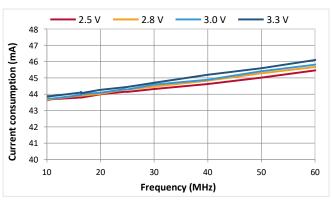

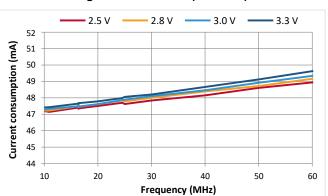

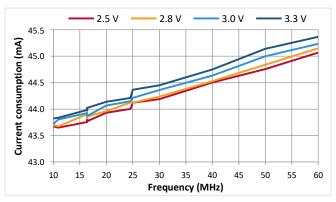

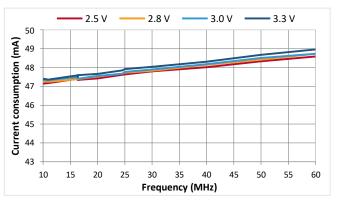

Figure 31. IDD TC-MO (LVCMOS)

Figure 32. IDD VCTC-MO (LVCMOS)

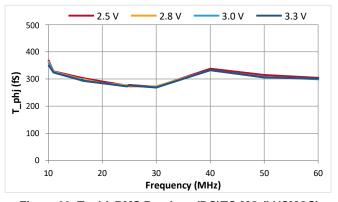

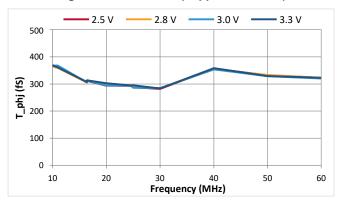

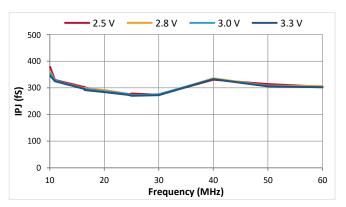

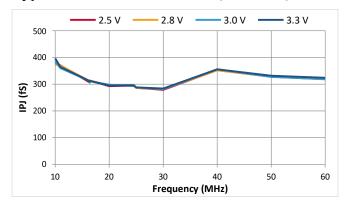

Figure 33. T\_phj, RMS Random, (DC)TC-MO (LVCMOS)

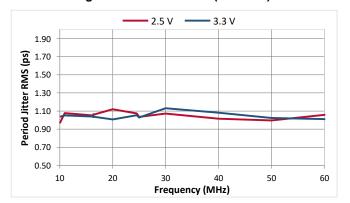

Figure 34. Period Jitter, RMS (LVCMOS)

# Typical Performance Plots (continued)

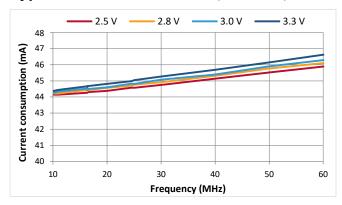

Figure 35. IDD DCTC-MO (LVCMOS)

Figure 37. DCTC-MO frequency pull characteristic

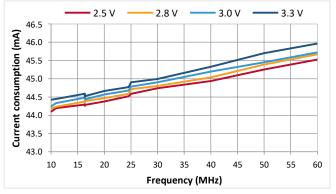

Figure 39. IDD TC-MO (Clipped Sinewave)

Figure 41. T\_phj, RMS Random, (DC)TC-MO (Clipped Sine)

Figure 36. T\_phj, RMS Random, VCTC-MO (LVCMOS)

Figure 38. Rise Time (Clipped Sinewave)

Figure 40. IDD VCTC-MO (Clipped Sinewave)

Figure 42. IDD DCTC-MO (Clipped Sinewave)

# Typical Performance Plots (continued)

Figure 43. T\_phj, RMS Random, VCTC-MO (Clipped Sine)

Figure 44. Duty Cycle (Clipped Sinewave)

### **Architecture Overview**

Based on KDS's innovative Elite Platform, the MO5358 delivers exceptional dynamic performance, i.e. resilience to environmental stressors such as shock, vibration and fast temperature transients. Underpinning the Elite platform are KDS's unique DualMEMS temperature sensing architecture and TurboCompensation technologies.

DualMEMS is a noiseless temperature compensation scheme. It consists of two MEMS resonators fabricated on the same die substrate. The TempFlat resonator is designed with a flat frequency characteristic over temperature whereas the temperature sensing resonator is by design sensitive to temperature changes. The ratio of frequencies between these two resonators provides an accurate reading of the resonator temperature with 20  $\mu K$  resolution.

By placing the two MEMS resonators on the same die, this temperature sensing scheme eliminates the thermal lag and gradients between the resonator and the temperature sensor, thereby overcoming an inherent weakness of the legacy quartz TCXOs.

The DualMEMS temperature sensor drives a state-of-theart CMOS temperature compensation circuit. The TurboCompensation design, with >100 Hz compensation bandwidth, achieves a dynamic frequency stability that is far superior to any quartz TCXO. The digital temperature compensation enables additional optimization of frequency stability and frequency slope over temperature within any chosen temperature range for a given system design.

Figure 45. Elite Architecture

The Elite platform also incorporates a high resolution, low noise frequency synthesizer along with the industry standard I<sup>2</sup>C bus. This unique combination enables system designers to digitally control the output frequency in steps as low as 5 ppt and over a wide range up to ±3200 ppm.

For more information regarding the Elite platform and its benefits please contact KDS.

#### **Functional Overview**

The MO5358 is designed for maximum flexibility with an array of factory programmable options, enabling system designers to configure this precision device for optimal performance in a given application.

#### Frequency Stability

The MO5358 comes in one factory-trimmed stability grade.

Table 12. Stability Grades vs. Ordering Codes

| Frequency Stability Over Temperature | Ordering Code |

|--------------------------------------|---------------|

| ±50 ppb                              | 3             |

### **Output frequency and format**

The MO5358 can be factory programmed for an output frequency without sacrificing lead time or incurring an upfront customization cost typically associated with custom-frequency quartz TCXOs.

The device supports both LVCMOS and clipped sinewave output. Ordering codes for the output format are shown below:

Table 13. Output Formats vs. Ordering Codes

| Output Format    | Ordering Code |

|------------------|---------------|

| LVCMOS           | "C"           |

| Clipped Sinewave | "၂"           |

#### **Output Frequency Tuning**

In addition to the non-pullable TC-MO, the MO5358 can also support output frequency tuning through either an analog control voltage (VCTC-MO), or  $\rm l^2C$  interface (DCTC-MO). The  $\rm l^2C$  interface enables 16 factory programmed pull-range options from  $\pm 6.25$  ppm to  $\pm 3200$  ppm. The pull range can also be reprogrammed via  $\rm l^2C$  to any supported pull-range value.

Refer to Device Configuration section for details.

### Pin 1 Configuration (OE, VC, or NC)

Pin 1 of the MO5358 can be factory-programmed to support three modes: Output Enable (OE), Voltage Control (VC) or No Connect (NC).

**Table 2. Pin Configuration Options**

| Pin 1 Configuration | Operating Mode | Output           |

|---------------------|----------------|------------------|

| OE                  | TC-MO/DCTC-MO  | Active or High-Z |

| NC                  | TC-MO/DCTC-MO  | Active           |

| VC                  | VCTC-MO        | Active           |

When pin 1 configured as OE pin, the device output is guaranteed to operate in one of the following two states:

- Clock output with the frequency specified in the part number when Pin 1 is pulled to logic high

- Hi-Z mode with weak pull down when pin 1 is pulled to logic low.

When pin 1 is configured as NC, the device is guaranteed to output the frequency specified in the part number at all times, regardless of the logic level on pin 1.

In the VCTC-MO configuration, the user can fine-tune the output frequency from the nominal frequency specified in the part number by varying the pin 1 voltage. The guaranteed allowable variation of the output frequency is specified as pull range. A VCTC-MO part number must contain a valid pull-range ordering code.

# **Device Configurations**

The MO5358 supports 3 device configurations – TC-MO, VCTC-MO and DCTC-MO. The TC-MO and VCTC-MO options are directly compatible with the quartz TCXO and VCTCXO. The DCTC-MO configuration provides performance enhancement by eliminating VCTC-MO's sensitivity to control voltage noise with an I<sup>2</sup>C digital interface for frequency tuning.

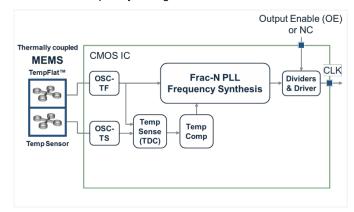

Figure 46. Block Diagram - TC-MO

#### **TC-MO Configuration**

The TC-MO configuration generates a fixed frequency output, as shown in Figure 46. The frequency is specified by the user in the frequency field of the device ordering code and then factory programmed. Other factory programmable options include supply voltage, output types (LVCMOS or clipped sinewave), and pin 1 functionality (OE or NC).

Refer to the ordering information section at the end of the datasheet for a list of all ordering options.

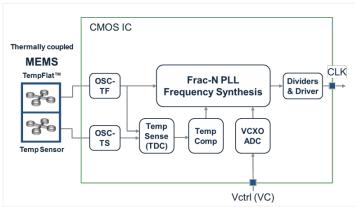

### **VCTC-MO Configuration**

A VCTC-MO, shown in Figure 47, is a frequency control device whose output frequency is an approximately linear function of control voltage applied to the voltage control pin. VCTC-MOs have a number of use cases including the VCO portion of a jitter attenuation/jitter cleaner PLL Loop.

The MO5358 achieves a 10x better pull range linearity of <0.5% via a high-resolution fractional PLL compared with 5% to 10% typical of quartz VCTCXOs that rely on pulling a resonator. By contrast, quartz-based VCTCXOs change output frequency by varying the capacitive load of a crystal resonator using varactor diodes, which results in poor linearity.

Figure 47. Block Diagram - VCTC-MO

Note that the output frequency of the VCTC-MO is proportional to the analog control voltage applied to pin 1. Because this control signal is analog and directly controls the output frequency, care must be taken to minimize noise on this pin.

The nominal output frequency is factory programmed per the customer's request to 6 digits of precision and is defined as the output frequency when the control voltage equals Vdd/2. The maximum output frequency variation from this nominal value is set by the pull range, which is also factory programmed to the customer's desired value and specified by the ordering code. The Ordering Information section shows all ordering options and associated ordering codes.

Refer to VCTCXO-Specific Design Considerations for more information on critical VCTC-MO parameters including pull range linearity, absolute pull range, control voltage bandwidth, and Kv.

#### **DCTC-MO Configuration**

The MO5358 offers digital control of the output frequency, as shown in Figure 48. The output frequency is controlled by writing frequency control words over the I<sup>2</sup>C interface.

There are several advantages of DCTC-MOs relative to VCTC-MOs:

- Frequency control resolution as low as 5 ppt. This high resolution minimizes accumulated time error in synchronization applications.

- Lower system cost A VCTC-MO may need a Digital to Analog Converter (DAC) to drive the control voltage input. In a DCTC-MO, the frequency control is achieved digitally by register writes to the control registers via I<sup>2</sup>C, thereby eliminating the need for a DAC.

- 3) Better noise immunity The analog signal used to drive the voltage control pin of a VCTC-MO can be sensitive to noise and the trace over which the signal is routed can be susceptible to noise coupling from the system. The DCTC-MO does not suffer from analog noise coupling since the frequency control is performed digitally through I<sup>2</sup>C.

- 4) No frequency pull non-linearity The frequency pulling is achieved via fractional feedback divider of the PLL, eliminating any pull non-linearity concerns typical of quartz based VCTCXOs. This improves dynamic performance in closed-loop operations.

- 5) Programmable wide pull range The DCTC-MO pulling mechanism is via the fractional feedback divider and is therefore not constrained by resonator pullability as in quartz based solutions. The MO5358 offers 16 frequency pull range options from ±6.25ppm to ±3200ppm, providing system designers great flexibility.

Refer to DCTCMO-Specific Design Considerations for more information on critical DCTC-MO parameters including pull range, absolute pull range, frequency output, and I<sup>2</sup>C control registers.

Figure 48. Block Diagram - DCTC-MO

### **VCTC-MO-Specific Design Considerations**

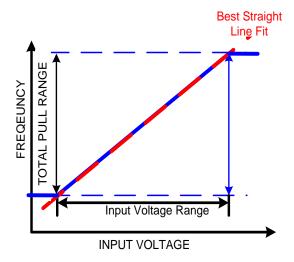

#### Linearity

In any VCTC-MO, there will be some deviation of the frequency-voltage (FV) characteristic from an ideal straight line. Linearity is the ratio of this maximum deviation to the total pull range, expressed as a percentage. Figure 49 below shows the typical pull linearity of a KDS VCTC-MO. The linearity is excellent (1% maximum) relative to most quartz offerings because the frequency pulling is achieved with a PLL rather than varactor diodes.

Figure 49. Typical KDS VCTC-MO Linearity

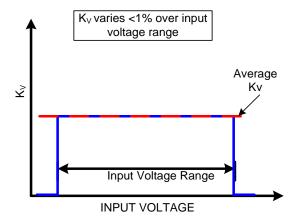

### **Control Voltage Bandwidth**

Control voltage bandwidth, sometimes called "modulation rate" or "modulation bandwidth", indicates how fast a VCO can respond to voltage changes at its input. The ratio of the output frequency variation to the input voltage variation, previously denoted by Kv, has a low-pass characteristic in most VCTC-MOs. The control voltage bandwidth equals the modulating frequency where the output frequency deviation equals 0.707 (e.g. -3 dB) of its DC value, for DC inputs swept in the same voltage range.

For example, a part with a  $\pm 6.25$  ppm pull range and a 0-3V control voltage can be regarded as having an average KV of 4.17 ppm/V (12.5 ppm/3V = 4.17 ppm/V). Applying an input of +1.5V DC  $\pm$  0.5V (+1.0 V to +2.0V) causes an output frequency change of 4.17 ppm ( $\pm 2.08$  ppm). If the control voltage bandwidth is specified as 10 kHz, the peak-to-peak value of the output frequency change will be reduced to 4.33 ppm/ $\sqrt{2}$  or 2.95 ppm, as the frequency of the control voltage change is increased to 10 kHz.

### FV Characteristic Slope K<sub>V</sub>

The slope of the FV characteristic is a critical design parameter in many low bandwidth PLL applications. The slope is the derivative of the FV characteristic – the deviation of frequency divided by the control voltage change needed to produce that frequency deviation, over a small voltage span, as shown below:

$$K_{V} = \frac{\Delta f_{out}}{\Delta V_{in}}$$

It is typically expressed in kHz/Volt, MHz/Volt, ppm/Volt, or similar units. This slope is usually called "Kv" based on terminology used in PLL designs.

The extreme linear characteristic of the KDS MO5358 VCTC-MO family means that there is very little K $_{\rm V}$  variation across the whole input voltage range (typically <1%), significantly reducing the design burden on the PLL designer. Figure 50 below illustrates the typical K $_{\rm V}$  variation.

Figure 50. Typical KDS K<sub>V</sub> Variation

# Pull Range, Absolute Pull Range

Pull range (PR) is the amount of frequency deviation that will result from changing the control voltage over its maximum range under nominal conditions.

Absolute pull range (APR) is the guaranteed controllable frequency range over all environmental and aging conditions. Effectively, it is the amount of pull range remaining after taking into account frequency stability tolerances over variables such as temperature, power supply voltage, and aging, i.e.:

$$APR = PR - F_{\text{stability}} - F_{\text{aging}}$$

where  $F_{\text{stability}}$  is the device frequency stability due to initial tolerance and variations on temperature, power supply, and load.

Figure 51 shows a typical KDS VCTC-MO FV characteristic. The FV characteristic varies with conditions, so that the frequency output at a given input voltage can vary by as much as the specified frequency stability of the VCTC-MO. For such VCTC-MOs, the frequency stability and APR are independent of each other. This allows very wide range of pull options without compromising frequency stability.

Figure 51. Typical KDS VCTC-MO FV Characteristic

The upper and lower control voltages are the specified limits of the input voltage range as shown on Figure 51 above. Applying voltages beyond the upper and lower voltages do not result in noticeable changes of output frequency. In other words, the FV characteristic of the VCTC-MO saturates beyond these voltages. Figures 1 and 2 show these voltages as Lower Control Voltage (VC\_L) and Upper Control Voltage (VC\_U).

Table 15 below shows the pull range and corresponding APR values for each of the frequency vs. temperature ordering options.

Table 15. VCTC-MO Pull Range, APR Options<sup>[11]</sup>

Typical unless specified otherwise. Pull range (PR) is ±6.25 ppm.

| Pull Range<br>Ordering Code | Device Option(s) | APR ppm<br>±50 ppb option<br>±0.5 ppm 20-year aging |

|-----------------------------|------------------|-----------------------------------------------------|

| Т                           | VCTC-MO          | ±5.2                                                |

#### Notes:

<sup>11.</sup> APR includes ±1 ppm solder down shift, frequency stability vs. temperature, and the corresponding 20-year aging.

# **DCTCXO-Specific Design Considerations**

# Pull Range and Absolute Pull Range

Pull range and absolute pull range are described in the previous section. Table 16 below shows the pull range and corresponding APR values for each of the frequency vs. temperature ordering options.

Table 16. APR Options<sup>[12]</sup>

| Pull Range Ordering Code | Pull Range ppm | APR ppm<br>±0.1 ppm option<br>±0.5 ppm 20-year aging |  |  |  |  |

|--------------------------|----------------|------------------------------------------------------|--|--|--|--|

| Т                        | ±6.25          | ±5.2                                                 |  |  |  |  |

| R                        | ±10            | ±8.95                                                |  |  |  |  |

| Q                        | ±12.5          | ±11.45                                               |  |  |  |  |

| M                        | ±25            | ±23.95                                               |  |  |  |  |

| В                        | ±50            | ±48.95                                               |  |  |  |  |

| С                        | ±80            | ±78.95                                               |  |  |  |  |

| E                        | ±100           | ±98.95                                               |  |  |  |  |

| F                        | ±125           | ±123.95                                              |  |  |  |  |

| G                        | ±150           | ±148.95                                              |  |  |  |  |

| Н                        | ±200           | ±198.95                                              |  |  |  |  |

| Х                        | ±400           | ±398.95                                              |  |  |  |  |

| L                        | ±600           | ±598.95                                              |  |  |  |  |

| Y                        | ±800           | ±798.95                                              |  |  |  |  |

| S                        | ±1200          | ±1198.95                                             |  |  |  |  |

| Z                        | ±1600          | ±1598.95                                             |  |  |  |  |

| U                        | ±3200          | ±3198.95                                             |  |  |  |  |

#### Notes:

<sup>12.</sup> APR includes initial tolerance, frequency stability vs. temperature, and the corresponding 20-year aging.

#### **Output Frequency**

The device powers up at the nominal operating frequency and pull range specified by the ordering code. After power- up both pull range and output frequency can be controlled via I<sup>2</sup>C writes to the respective control registers. The maximum output frequency change is constrained by the pull range limits.

The pull range is specified by the value loaded in the digital pull-range control register. The 16 pull range choices are specified in the control register and range from ±6.25ppm to ±3200ppm.

Table 17 below shows the frequency resolution versus pull range programmed value

Table 17. Frequency Resolution vs. Pull Range

| Programmed Pull Range | Frequency Resolution  |

|-----------------------|-----------------------|

| ±6.25ppm              | 5x10 <sup>-12</sup>   |

| ±10ppm                | 5x10 <sup>-12</sup>   |

| ±12.5ppm              | 5x10 <sup>-12</sup>   |

| ±25ppm                | 5x10 <sup>-12</sup>   |

| ±50ppm                | 5x10 <sup>-12</sup>   |

| ±80ppm                | 5x10 <sup>-12</sup>   |

| ±100ppm               | 5x10 <sup>-12</sup>   |

| ±120ppm               | 5x10 <sup>-12</sup>   |

| ±150ppm               | 5x10 <sup>-12</sup>   |

| ±200ppm               | 5x10 <sup>-12</sup>   |

| ±400ppm               | 1x10 <sup>-11</sup>   |

| ±600ppm               | 1.4x10 <sup>-11</sup> |

| ±800ppm               | 2.1x10 <sup>-11</sup> |

| ±1200ppm              | 3.2x10 <sup>-11</sup> |

| ±1600ppm              | 4.7x10 <sup>-11</sup> |

| ±3200ppm              | 9.4x10 <sup>-11</sup> |

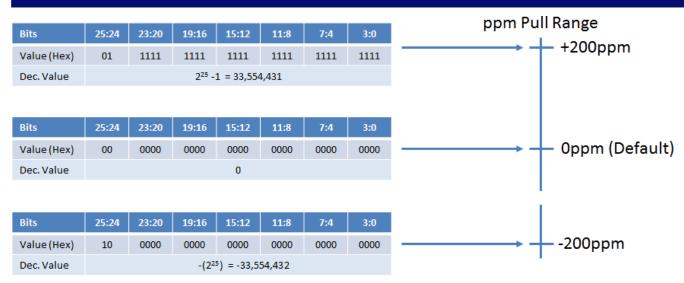

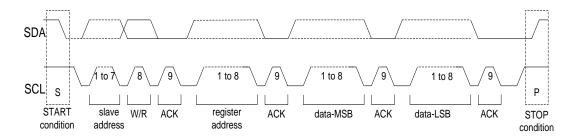

The ppm frequency offset is specified by the 26 bit DCXO frequency control register in two's complement format as described in the I²C Register Descriptions. The power up default value is 000000000000000000000000000 which sets the output frequency at its nominal value (0 ppm). To change the output frequency, a frequency control word is written to 0x00[15:0] (Least Significant Word) and 0x01[9:0] (Most Significant Word). The LSW value should be written first followed by the MSW value; the frequency change is initiated after the MSW value is written.

Figure 52 Pull range and Frequency Control Word

Figure 52 shows how the two's complement signed value of the frequency control word sets the output frequency within the ppm pull range set by 0x02:[3:0]. This example shows use of the ±200 ppm pull range. Therefore, to set the desired output frequency, one just needs to calculate the fraction of full scale value ppm, convert to two's complement binary and then write the values to the frequency control registers.

The following formula generates the control word value:

Control word Value = RND(( $2^{25}$ -1) x ppm shift from nominal/pull range), where RND is the rounding function which rounds the number to the nearest whole number. Two examples follow, assuming the  $\pm 200$  ppm pull range:

#### Example 1:

- Default Output Frequency = 19.2 MHz

- Desired Output Frequency = 19.201728 MHz (+90 ppm)

$2^{25}$ -1 corresponds to +200 ppm, and the fractional value required for +90 ppm can be calculated as follows.

$\blacksquare$  90 ppm / 200 ppm x (2<sup>25</sup>-1) = 15,099,493.95.

Rounding to the nearest whole number yields 15,099,494 and converting to two's complement gives a binary value of 111001100110011001100110 and E66666 in hex.

#### Example 2:

- Default Output Frequency = 10 MHz

- Desired Output Frequency = 9.998 MHz (-50 ppm)

Following the formula shown above,

$\blacksquare$  (-50 ppm / 200 ppm) x (2<sup>25</sup>-1) = -8,388,607.75.

Rounding this to the nearest whole number results in -8,388,608.

To summarize, the procedure for calculating the frequency control word associated with a given ppm offset is as follows:

- Calculate the fraction of the half pull range needed. For example, if the total pull range is set for ±100 ppm and a +20 ppm shift from the nominal frequency is needed, this fraction is 20 ppm/100 ppm = 0.2

- 2) Multiply this fraction by the full half scale word value,  $2^{25}$ -1 = 33,554,431, round to the nearest whole number and convert the result to two's complement binary. Following the +20ppm example, this value is 0.2 x 33,554,431 = 6,710,886.2 and rounded to 6,710,886.

- Write the two's complement binary value starting with the Least Significant Word (LSW) 0x00[16:0], followed by the Most Significant Word (MSW), 0x01[9:0]. If the user desires that the output remains enabled while changing the frequency, a 1 must also be written to the OE control bit 0x01[10] if the device has software OE Control Enabled.

It is important to note that the maximum Digital Control update rate is 38 kHz regardless of I<sup>2</sup>C bus speed.

# I<sup>2</sup>C Control Registers

The MO5358 enables control of frequency pull range, frequency pull value, and Output Enable via I<sup>2</sup>C writes to the control registers. Table 18 below shows the register map summary, and detailed register descriptions follow.

### **Table 18. Register Map Summary**

| Address | Bits    | Access | Description                                                                                                                                                                                        |

|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00    | [15:0]  | RW     | DIGITAL FREQUENCY CONTROL LEAST SIGNIFICANT WORD (LSW)                                                                                                                                             |

| 0x01    | [15:11] | R      | NOT USED                                                                                                                                                                                           |

|         | [10]    | RW     | OE Control. This bit is only active if the output enable function is under software control. If the device is configured for hardware control using the OE pin, writing to this bit has no effect. |

|         | [9:0]   | RW     | DIGITAL FREQUENCY CONTROL MOST SIGNIFICANT WORD (MSW)                                                                                                                                              |

| 0x02    | [15:4]  | R      | NOT USED                                                                                                                                                                                           |

|         | [3:0]   | RW     | DIGITAL PULL RANGE CONTROL                                                                                                                                                                         |

# **Register Descriptions**

# Register Address: 0x00. Digital Frequency Control Least Significant Word (LSW)

| Bit     | 15 | 14                                                           | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|--------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Access  | RW | RW                                                           | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW | RW |

| Default | 0  | 0                                                            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Name    |    | DIGITAL FREQUENCY CONTROL LEAST SIGNIFICANT WORD (LSW)[15:0] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Bits | Name                                                   | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | DIGITAL FREQUENCY<br>CONTROL LEAST<br>SIGNIFICANT WORD | RW     | Bits [15:0] are the lower 16 bits of the 26 bit FrequencyControlWord and are the Least Significant Word (LSW). The upper 10 bits are in regsiter 0x01[9:0] and are the Most Significant Word (MSW). The lower 16 bits together with the upper 10 bits specify a 26-bit frequency control word.  This power-up default values of all 26 bits are 0 which sets the output frequency at its nominal value. After power-up, the system can write to these two registers to pull the frequency across the pull range. The register values are two's complement to support positive and negative control values. The LSW value should be written before the MSW value because the frequency change is initiated when the new values are loaded into the MSW. More details and examples are discussed in the next section. |

# Register Address: 0x01. OE Control, Digital Frequency Control Most Significant Word (MSW)

| Bit     | 15 | 14 | 13      | 12 | 11 | 10 | 9  | 8  | 7   | 6      | 5      | 4      | 3         | 2  | 1  | 0  |

|---------|----|----|---------|----|----|----|----|----|-----|--------|--------|--------|-----------|----|----|----|

| Access  | R  | R  | R       | R  | R  | RW | RW | RW | RW  | RW     | RW     | RW     | RW        | RW | RW | RW |

| Default | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0   | 0      | 0      | 0      | 0         | 0  | 0  | 0  |

| Name    |    | N  | IOT USE | D  |    | OE |    |    | DC- | MO FRE | QUENCY | CONTRO | DL[9:0] M | SW |    |    |

| Bits  | Name                                                     | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------|----------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 15:11 | NOT USED                                                 | R      | Bits [15:10] are read only and return all 0's when read. Writing to these bits has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 10    | OE Control                                               | RW     | Output Enable Software Control. Allows the user to enable and disable the output driver via I <sup>2</sup> C.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|       |                                                          |        | 0 = Output Disabled (Default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|       |                                                          |        | 1 = Output Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|       |                                                          |        | This bit is only active if the Output Enable function is under software control. If the device is configured for hardware control using the OE pin, writing to this bit has no effect.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |