#### Features

- Any frequency between 220 MHz and 625 MHz accurate to 6 decimal places

- LVPECL and LVDS output signaling types

- 0.6ps RMS phase jitter (random) over 12 kHz to 20 MHz bandwidth

- Frequency stability as low as ±10 ppm

- Industrial and extended commercial temperature ranges

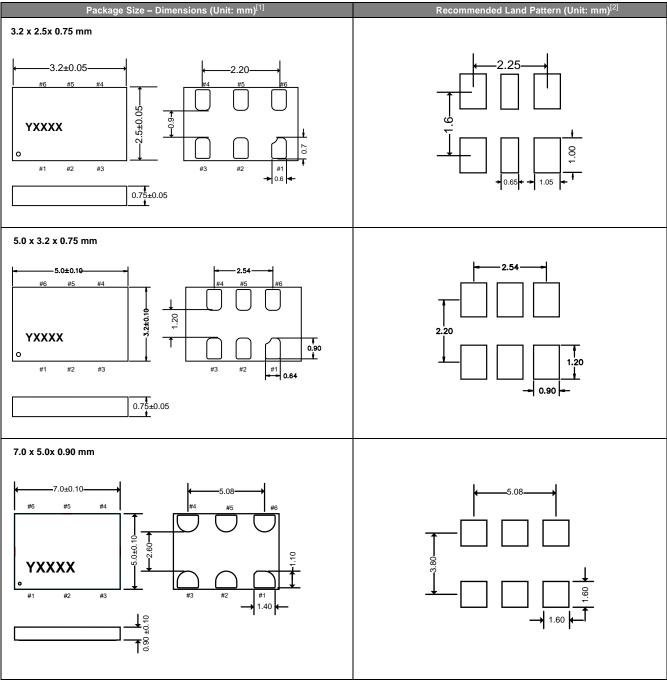

- Industry-standard packages: 3.2x2.5, 5.0x3.2 and 7.0x5.0 mmxmm

- For frequencies lower than 220 MHz, refer to MO9121 datasheet

# **Electrical Characteristics**

# Applications

- 10GB Ethernet, SONET, SATA, SAS, Fibre Channel, PCI-Express

- Telecom, networking, instrumentation, storage, servers

| Parameter and Conditions          | Symbol     | Min.    | Тур.      | Max.       | Unit       | Condition                                                          |

|-----------------------------------|------------|---------|-----------|------------|------------|--------------------------------------------------------------------|

|                                   |            |         |           |            | ectrical C | characteristics                                                    |

|                                   | _          | +2.97   | +3.3      | +3.63      | V          |                                                                    |

| Supply Voltage                    | Vdd        | +2.25   | +2.5      | +2.75      | V          |                                                                    |

| Supply Vollage                    | vuu        | +2.25   | -         | +3.63      | V          | Termination schemes in Figures 1 and 2 - XX ordering code          |

| Output Frequency Range            | f          | 220     | _         | 625        | MHz        |                                                                    |

|                                   |            | -10     | _         | +10        | ppm        |                                                                    |

|                                   | F_stab     | -20     | _         | +20        | ppm        | Inclusive of initial tolerance, operating temperature, rated power |

| Frequency Stability               |            | -25     | _         | +25        | ppm        | supply voltage, and load variations                                |

|                                   |            | -50     | _         | +50        | ppm        | -                                                                  |

| First Year Aging                  | F_aging1   | -2.0    | _         | +2.0       | ppm        | +25°C                                                              |

| 10-year Aging                     | F_aging10  | -5.0    | _         | +5.0       | ppm        | +25°C                                                              |

|                                   | agiiig i o | -40     | _         | +85        | °C         | Industrial                                                         |

| Operating Temperature Range       | T_use      | -20     | _         | +70        | °C         | Extended ST                                                        |

| Input Voltage High                | VIH        | 70%     | _         | -          | Vdd        | Pin 1, OE or ST                                                    |

|                                   |            |         |           |            |            |                                                                    |

| Input Voltage Low                 | VIL        | -       | -         | 30%        | Vdd        | Pin 1, OE or ST                                                    |

|                                   | Z in       | -       | 100       | 250        | kΩ         | Pin 1, OE logic high or logic low, or ST logic high                |

| Input Pull-up Impedance           |            | 2.0     | -         | -          | MΩ         | Pin 1, ST logic low                                                |

| Start-up Time                     | T_start    | -       | 6.0       | 10         | ms         | Measured from the time Vdd reaches its rated minimum value.        |

| Resume Time                       | T_resume   | _       |           | 10         | ms         | In Standby mode, measured from the time ST pin                     |

|                                   |            |         |           |            |            | crosses 50% threshold.                                             |

| Duty Cycle                        | DC         | 45      | -         | 55         | %          | Contact KDS for tighter dutycycle                                  |

|                                   |            | L       | VPECL, DO | C and AC C | Characteri | stics                                                              |

| Current Consumption               | ldd        | -       | +61       | +69        | mA         | Excluding Load Termination Current, Vdd = 3.3V or 2.5V             |

| OE Disable Supply Current         | I_OE       | -       | -         | +35        | mA         | OE = Low                                                           |

| Output Disable Leakage Current    | I_leak     | -       | -         | +1.0       | μA         | OE = Low                                                           |

| Standby Current                   | I_std      | -       | -         | +100       | μΑ         | $\overline{ST}$ = Low, for all Vdds                                |

| Maximum Output Current            | I_driver   | _       | -         | +30        | mA         | Maximum average current drawn from OUT+ or OUT-                    |

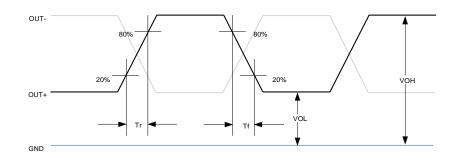

| Output High Voltage               | VOH        | Vdd-1.1 | -         | Vdd-0.7    | V          | See Figure 1(a)                                                    |

| Output Low Voltage                | VOL        | Vdd-1.9 | Ι         | Vdd-1.5    | V          | See Figure 1(a)                                                    |

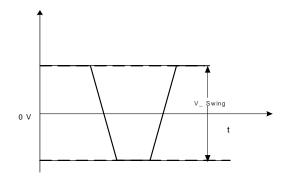

| Output Differential Voltage Swing | V_Swing    | +1.2    | +1.6      | +2.0       | V          | See Figure 1(b)                                                    |

| Rise/Fall Time                    | Tr, Tf     | -       | 300       | 500        | Ps         | 20% to 80%, see Figure 1(a)                                        |

| OE Enable/Disable Time            | T_oe       | -       | -         | 115        | Ns         | f = 220 MHz - For other frequencies, T_oe = 100ns + 3 period       |

|                                   |            | -       | 1.2       | 1.7        | Ps         | f = 266 MHz, Vdd = +3.3V or +2.5V                                  |

| RMS Period Jitter                 | T_jitt     | -       | 1.2       | 1.7        | Ps         | f = 312.5 MHz, Vdd = +3.3V or +2.5V                                |

|                                   |            | -       | 1.2       | 1.7        | Ps         | f = 622.08 MHz, Vdd = +3.3V or +2.5V                               |

| RMS Phase Jitter (random)         | T_phj      | -       | 0.6       | 0.85       | Ps         | f = 312.5 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdds  |

|                                   | 1          |         | LVDS, DC  | and AC Ch  | aracteris  |                                                                    |

| Current Consumption               | ldd        | -       | +47       | +55        | mA         | Excluding Load Termination Current, Vdd = +3.3V or +2.5V           |

| OE Disable Supply Current         | I_OE       | -       | -         | +35        | mA         | OE = Low                                                           |

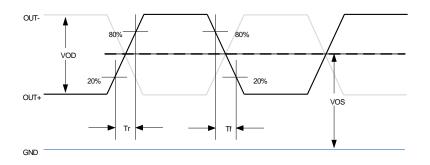

| Differential Output Voltage       | VOD        | +250    | +350      | +450       | mV         | See Figure 2                                                       |

#### Electrical Characteristics(continued)

| Parameter and Conditions                                   | Symbol | Min.   | Тур. | Max.   | Unit     | Condition                                                         |  |

|------------------------------------------------------------|--------|--------|------|--------|----------|-------------------------------------------------------------------|--|

| LVDS, DC and AC Characteristics (continued)                |        |        |      |        |          |                                                                   |  |

| Output Disable Leakage Current I_leak – – +1.0 µA OE = Low |        |        |      |        | OE = Low |                                                                   |  |

| Standby Current                                            | I_std  | -      | -    | +100   | μA       | $\overline{ST}$ = Low, for all Vdds                               |  |

| VOD Magnitude Change                                       | ΔVOD   | -      | -    | +50    | mV       | See Figure 2                                                      |  |

| Offset Voltage                                             | VOS    | +1.125 | +1.2 | +1.375 | V        | See Figure 2                                                      |  |

| VOS Magnitude Change                                       | ΔVOS   | -      | -    | +50    | mV       | See Figure 2                                                      |  |

| Rise/Fall Time                                             | Tr, Tf | -      | 495  | 600    | ps       | 20% to 80%, see Figure 2                                          |  |

| OE Enable/Disable Time                                     | T_oe   | -      | -    | 115    | ns       | f = 220 MHz - For other frequencies, T_oe = 100ns + 3 period      |  |

|                                                            |        | -      | 1.4  | 1.7    | ps       | f = 266 MHz, Vdd = +3.3V or +2.5V                                 |  |

| RMS Period Jitter                                          | T_jitt | -      | 1.4  | 1.7    | ps       | f = 312.5 MHz, Vdd = +3.3V or +2.5V                               |  |

|                                                            |        | -      | 1.2  | 1.7    | ps       | f = 622.08 MHz, Vdd = +3.3V or +2.5V                              |  |

| RMS Phase Jitter (random)                                  | T_phj  | -      | 0.6  | 0.85   | ps       | f = 312.5 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdds |  |

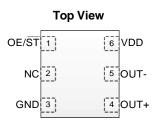

### **Pin Description**

| Pin | Мар  | Functionality |                                                                                                         |  |  |  |  |

|-----|------|---------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | OE   | Input         | H or Open: specified frequency output<br>L: output is high impedance                                    |  |  |  |  |

| 1   | ST   | Input         | H or Open: specified frequency output<br>L: Device goes to sleep mode. Supply current reduces<br>I_std. |  |  |  |  |

| 2   | NC   | NA            | No Connect; Leave it floating or connect to GND for better heat dissipation                             |  |  |  |  |

| 3   | GND  | Power         | VDD Power Supply Ground                                                                                 |  |  |  |  |

| 4   | OUT+ | Output        | Oscillator output                                                                                       |  |  |  |  |

| 5   | OUT- | Output        | Complementary oscillator output                                                                         |  |  |  |  |

| 6   | VDD  | Power         | Power supply voltage                                                                                    |  |  |  |  |

#### Absolute Maximum

Attempted operation outside the absolute maximum ratings of the part may cause permanent damage to the part. Actual perfor- mance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Min. | Max.  | Unit |

|----------------------------------------------------------------------|------|-------|------|

| StorageTemperature                                                   | -65  | +150  | °C   |

| VDD                                                                  | -0.5 | +4.0  | V    |

| Electrostatic Discharge (HBM)                                        | _    | +2000 | V    |

| Soldering Temperature (follow standard Pb free soldering guidelines) | -    | +260  | °C   |

#### **Thermal Consideration**

| Package     | θJA, 4 Layer Board<br>(°C/W) | θJC, Bottom<br>(°C/W) |

|-------------|------------------------------|-----------------------|

| 7050, 6-pin | 142                          | 27                    |

| 5032, 6-pin | 97                           | 20                    |

| 3225, 6-pin | 109                          | 20                    |

# **Environmental Compliance**

| Parameter                  | Condition/Test Method    |

|----------------------------|--------------------------|

| Mechanical Shock           | MIL-STD-883F, Method2002 |

| Mechanical Vibration       | MIL-STD-883F, Method2007 |

| Temperature Cycle          | JESD22, Method A104      |

| Solderability              | MIL-STD-883F, Method2003 |

| Moisture Sensitivity Level | MSL1 @ 260°C             |

# **Waveform Diagrams**

Figure 1(a). LVPECL Voltage Levels per Differential Pin (OUT+/OUT-)

Figure 1(b). LVPECL Voltage Levels Across Differential Pair

Figure 2. LVDS Voltage Levels per Differential Pin (OUT+/OUT-)

### **Termination Diagrams**

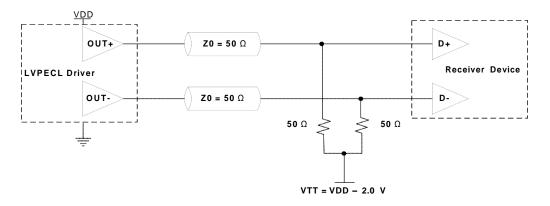

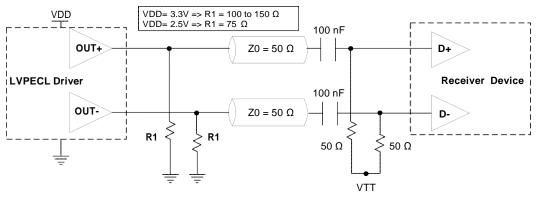

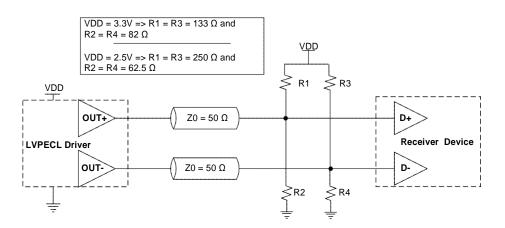

#### LVPECL:

Figure 3. LVPECL Typical Termination

Figure 4. LVPECL AC Coupled Termination

Figure 5. LVPECL with Thevenin Typical Termination

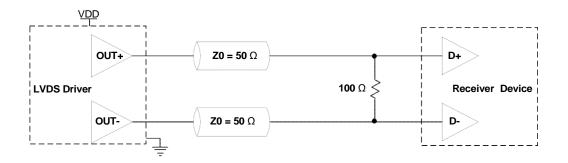

LVDS:

Figure 6. LVDS Single Termination (Load Terminated)

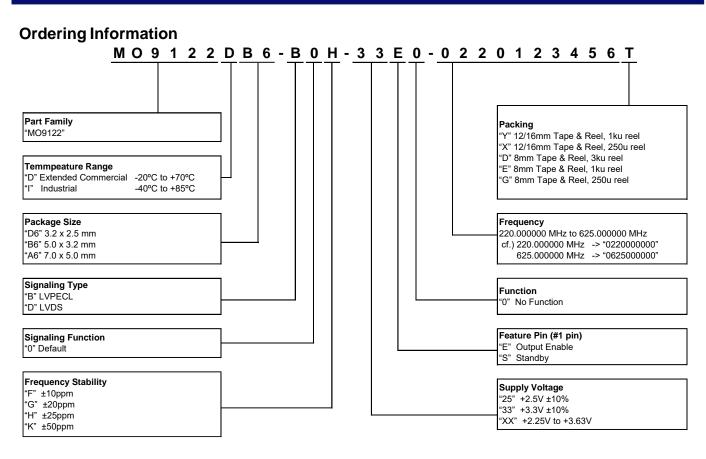

#### **Dimensions and Patterns**

#### Notes:

Top Marking: Y denotes manufacturing origin and XXXX denotes manufacturing lot number. The value of "Y" will depend on the assembly location of the device.

A capacitor of value 0.1 μF between Vdd and GND is recommended.

# **Frequencies Not Supported**

| Range 1: From 251.000001 MHz to 263.999999MHz  |

|------------------------------------------------|

| Range 2: From 314.000001 MHz to 422.999999MHz  |

| Range 3: From 502.000001 MHz to 527.999999 MHz |

#### **Ordering Codes for Supported Tape & Reel Packing Method**

| Device Size  | 8 mm T&R<br>(3ku) | 8 mm T&R<br>(1ku) | 8 mm T&R<br>(250u) | 12 mm T&R<br>(1ku) | 12 mm T&R<br>(250u) | 16 mm T&R<br>(1ku) | 16 mm T&R<br>(250u) |

|--------------|-------------------|-------------------|--------------------|--------------------|---------------------|--------------------|---------------------|

| 7.0 x 5.0 mm | -                 | -                 | -                  | -                  | -                   | Y                  | Х                   |

| 5.0 x 3.2 mm | -                 | -                 | -                  | Y                  | Х                   | -                  | -                   |

| 3.2 x 2.5 mm | D                 | E                 | G                  | -                  | -                   | -                  | -                   |

# **Revision History**

| Version | Release Date | Change Summary                                                           |  |  |  |

|---------|--------------|--------------------------------------------------------------------------|--|--|--|

| 1.01    | 2/20/13      | Original                                                                 |  |  |  |

| 1.02    | 12/3/13      | Added input specifications, LVPECL/LVDS waveforms, packaging T&R options |  |  |  |

| 1.03    | 2/6/14       | Added 8mm T&R option and ±10 ppm                                         |  |  |  |

| 1.04    | 7/23/14      | Include Thermal Consideration Table                                      |  |  |  |

| 1.05    | 10/6/14      | Modified Thermal Consideration values                                    |  |  |  |